| |

| ÷™ ∂ø‚ -> ˝¬Î -> Œ“π˙Œ™ ≤√¥≤ªÕ∆π„¡˙–æ£ø -> ’˝Œƒ‘ƒ∂¡ |

|

|

[ ˝¬Î]Œ“π˙Œ™ ≤√¥≤ªÕ∆π„¡˙–æ£ø |

| [ ’≤ÿ±æŒƒ] °æœ¬‘ÿ±æŒƒ°ø |

|

¡˙–æœ÷‘⁄ø¥±®µ¿”¶∏√”–»¸—ÔJ1800ªÚ’þ∏¸«øµƒ–‘ƒÐ¡À£¨À‰»ª≤ªƒÐ”√windows£¨µ´ «–Ì∂ý∞Ïπ´µƒµÿ∑Ω“≤≤ª¥Ú”Œœ∑£¨æÕ «ºÚµ•µƒ”√∞Ïπ´»Ìº˛£¨“≤–ÌœÒ∏ˆ±≤∆ŒÒ≤ø√≈µ»°≠ |

|

º∏∏ˆ∏˘±æ–‘µƒŒ Â: ºÊ»ð–‘ ¡˙–æ∂º « MIPS, µ´ «◊˜Œ™ MIPS ¿¥Àµ, À˚µƒÃÿ–‘”÷≤ªÕÍ»´ºÊ»ð∆‰À˚ MIPS: ◊˜’þ£∫“¢“‘ø°µ¬ ¡¥Ω”£∫https://www.zhihu.com/question/48881215/answer/518741822 “ªø™ º «∑¢œ÷ gobject-introspection ª·À¿À¯£®√ª”–∑¥”¶£¨∞¥ ^C ø…ÕÀ≥ˆ£©£¨Œ“√«“≤√ª”–’“µΩΩ‚æˆ∑Ω∞∏£¨æÕ‘ð«“πÿµÙ¡À“ª–© GTK ∞¸µƒŒƒµµππΩ®°£∫Û¿¥∑¢œ÷≤ø∑÷±µƒ”¶”√“≤ª·À¿À¯£¨Œ“√«æÕø™ º gdb ø¥Œ £¨’“µΩŒ Âœð‘⁄ FFmpeg µƒø‚¿Ô£¨”⁄ «Œ“√«”÷»•’“ «≤ª « FFmpeg µƒππΩ®≈‰÷√≤ª∂‘£¨ø™¥Ì¡À ≤√¥ø™πÿ°£’“¡À∞ÎÃÏ£® µº …œ”–“ª∏ˆ‘¬£©∂º≤ª÷™µ¿Œ™ ≤√¥ª·œð»ÎÀ¿À¯£¨◊Ó∫Û∞— Glibc µƒµ˜ ‘–≈œ¢¥Úø™∑¢œ÷¥˙¬Îœð‘⁄¡À pthread ¿Ô£¨∂¯ pthread ¥À ±’˝«…÷¥––µΩ¡À“ª∂Œ MIPS ÷∏¡Ó÷–µƒ Load Link / Store Conditional£®ll / sc£©÷∏¡Ó∂‘°£µΩ¡À’‚¿ÔŒ“√«≤≈“‚ ∂µΩŒ“√«≈ˆµΩ¡À”≤º˛Œ £∫‘⁄¡˙–æ 3 ∫≈÷–£¨√ø¥Œ÷¥–– ll ÷∏¡Ó÷Æ«∞“ª∂®“™÷¥––“ª¥Œ sync£¨≤¢«“ ll ÷∏¡Ó÷Æ∫Û sc ÷∏¡Ó÷Æ«∞µƒ¥˙¬Î»Áπ˚”–ï◊™£¨Ã¯◊™ƒø±Í“ª∂® « sync ÷∏¡Ó°£∆‰÷–«∞’þ–Ë“™¥Ú…œ GCC ∫Õ Binutils ≤π∂°£¨∫Û’þ–Ë“™¥˙¬Î◊‘––Ã̺”°£[5] ’‚∏ˆŒ Â÷˜“™”∞œÏ FFmpeg£¨À˘“‘À˘”–“¿¿µ FFmpeg µƒ»Ìº˛∂ºª·∏˜÷÷À¿À¯£¨FFmpeg ◊‘º∫¥¯µƒ√¸¡Ó‘Ú∏˜÷÷ SIGBUS°¢SIGILL ∫Õ SIGSEGV£¨◊Ó∫Û’˚∏ˆ∂ý√ΩÃÂ’ªª˘±æ…œ∂º «ªµµƒ£¨µ´ «≤ª“¿¿µ FFmpeg µƒ»Ìº˛≈е√ªπ «Õ¶ª∂µƒ°£ ffmpeg «“ª∏ˆ∂ý√ΩÃÂπ§æþ/ø‚, ∫Ð∂ý»ÌΩ‚≤•∑≈∆˜/OBS ’‚—˘µƒ∂ý√ΩÔ¶”√∂º“¿¿µÀ˚. ’‚∏ˆŒ ÂÀµ¥Û≤ª¥Û, µ´ «Àµ–°“≤≤ª–°, “ÚŒ™“‚Œ∂◊≈∫Ð∂ý√ÊœÚ MIPS-Linux µƒ”¶”√æÕ“™Œ™¥Àµ•∂¿∑¢≤º“ª∏ˆ∞ʱæ. ¡ÌÕ‚æÕ «œ‘»ª≤ªƒÐ‘≠…˙ºÊ»ð x86 ”¶”√. À‰ÀµÕ®π˝ qemu Ω¯––øÁ∆Ωî ISA ƒ£ƒ‚, »ª∫Û‘À–– wine æÕƒÐπª≈Ð∆¿¥≤Ó≤ª∂ý∆þ∞À≥…µƒ Windows ‘≠…˙”¶”√... µ´ «–‘ƒÐæÕ∫Ð∏–»À¡À. “™÷™µ¿ x86 …œ «ø…“‘º∏∫ı“‘ 100% …ı÷¡≥¨π˝ 100%(Linux wine ‘⁄ IO …œ√Ê”––© µœ÷ «“Ï≤Ω∑«◊Ë»˚µƒ) –‘ƒÐ‘À–– Windows ”¶”√. Linux ∑Ω√Ê”–÷˜œþ, GPU ”√ AMD + ø™‘¥«˝∂صƒæÕÀ„ «√„«øƒÐ”√¡À. 2. –‘ƒÐ ≤“. J1800 ‘⁄ Windows …œ“≤æÕ «º∏∫ı≤ªƒÐ”√µƒÀÆ∆Ω(œ÷‘⁄ƒÐ”√µƒµ◊œþ « J5005 ªÚ’þ 4415Y). »Áπ˚÷ª «√„«ø”Î∆‰≥÷∆Ω, ø…“‘œÎœÛ¥Û∂ý ˝ƒÐ≈еƒ∞Ïπ´»Ìº˛, libreoffice, ªÚ’þƒƒÃÏ“∆÷≤¡À WPS, ª˘±æ…œ≈Ð≤ª∂Ø. Office ◊þ–ȃ‚ªØ+wine µƒª∞π¿º∆≈Ð 03 ∂º≥‘¡¶. ƒÐ–ß…œÕÍ»´µƒµÊµ◊. 3. ºØ≥…∂» ∫Õ J1800 Ω”Ω¸µƒ–‘ƒÐµƒ¥˙º€ « ˝±∂µƒπ¶∫ƒ, Õ‚º” CPU die …œ≤ªºØ≥…ƒœ±±«≈∫Õ GPU. ÷Æ«∞æÕ±ª HT µƒ AMD –æ∆¨◊È∂œπ©’€Ã⁄¡À∫√æ√. 4. …˙è ◊œ» nix …œµƒ◊¿√Ê≤ª «ª˘”⁄π≈¿œµƒ X æÕ «ª˘”⁄ Wayland. »ª∫Û’‚–©◊¿√ÊœµÕ≥∫Õƒ⁄∫ÀµƒÒÓ∫œ∂»≤ª∏þ. √ø“ª∏ˆª˘±æ∂º «¥’∫œ◊≈”√µƒÀÆ∆Ω. ∂¯÷Æ«∞“≤Àµ¡À, »Áπ˚“™ƒÐ≈Ð, ª˘±æµ√µ»µΩ‘≠…˙∂˛Ω¯÷∆. ƒ«ø…“‘œÎœÛ’ʵƒ√ª…∂∂´Œ˜∫√≈СÀ. æÕÀ„ Chrome/Firefox ƒÐ≈Ð, ’‚–‘ƒÐ“≤∑«≥£≤“... ªπ”–, ∏ˆ±’˛∏ƪ˙πÿµƒÕ¯’æªπ”– IE Only, “‘º∞“¿¿µ Flash°¢ActiveX ∫Õ SliverLight ¿©’πµƒ... 5. º€∏Ò “ª∏ˆ–‘ƒÐΩ”Ω¸ J1800 µƒ∂´Œ˜, ª˘±ææÕ“™¬ÙµΩ 3000 µΩ 4000 ∂ý... J1800 ’‚÷÷÷ª“™ 300 æÕƒÐ∏„∂®÷˜∞Â, 500 ∏„∂®’˚ª˙, ªπ « thin itx... ∂¯¡˙–æ’‚±þ‘ı√¥∏„“≤÷ªƒÐ◊ˆµΩ matx... |

|

‘ı√¥Õ∆π„£¨Œ“Àʱ„¥Ú∏ˆ±»∑Ω£¨ƒ„ø¥ø¥øø∆◊≤ª£¨ƒÐ≤ªƒÐÃ◊”√‘⁄¡˙–æ…œ£∫ ¿œ∞Ÿ–’£∫ ≤√¥ÕÊ“‚£¨”÷ƒ—”√”÷πÛ£¨¿œ◊”≤≈≤ª¬Úƒÿ£¨’˛∏Æ∑ˆ≥÷µƒ»√’˛∏Æ°¢ª˙πÿ°¢ ¬“µµ•Œª°¢π˙∆Û°¢—Î∆Ûœ»µ±–°∞◊ Û»•°£ ÷–—Î’˛∏Æ£∫◊Ð≤ªƒÐ»√Œ“œ» ‘∞…£¨ÕÚ“ª≥ˆµ„ ≤√¥Œ ƒ«æÕÕ͵∞¡À£¨Œ“∂º «”√◊ÓŒ»∂®µƒ∂´Œ˜£¨≤ª«Û–¬≤ª«ÛøÏ≤ª«ÛπÛº˙£¨’‚–©–¬≥ˆµƒÕÊ“‚ƒ„ªπ «»√±»À ‘∫√ ‘Œ»∂®¡À‘Ÿ¿¥∞…£° µÿ∑Ω’˛∏Æ£∫ ’‚ÕÊ“‚∂˘ «‘€√«∑ˆ≥÷µƒ¬£ø≤ª «—Ω£ø≤ª «µƒª∞À≠∑ˆ≥÷µƒÀ≠œÎ∞Ï∑®»•£¨Œ“√«œ»µ±–°∞◊ Û£¨≥ˆ¡ÀŒ Â’‚∞Â◊”¥ÚÀ≠…Ì…œ£ø‘ŸÀµ¡À£¨…œº∂∂º≤ª∏“”√£¨Àµ√˜’‚ÕÊ“‚∂˘≤ªøø∆◊£¨Œ“√«Œ™…∂“™”√£¨”÷”–∑Áœ’”÷√ª∫√¥¶£¨’‚ ¬∂˘≤ª∏…°£ ’‚ÕÊ“‚∂˘ «‘€√«∑ˆ≥÷µƒ¬£ø «∞°£°ƒ«»√œ¬√Êœ» ‘ ‘∞…£¨ƒ«√¥∂ýª˙πÿ°¢π˙∆Û£¨ÃÙº∏∏ˆœ» ‘ ‘°£ œ¬º∂ª˙πÿ°¢π˙∆Û£∫ ”÷Õ∆π„–¬∂´Œ˜¡À£ø…œº∂≈˙◊ Ω¬£ø√ª≈˙£øƒ«’‚ ¬∂˘∏…≤ª¡À°£ ”÷Õ∆π„–¬∂´Œ˜¡À£ø…œº∂≈˙◊ Ω¬£øæ”»ª≈˙¡À£°ƒ«¬Úµ„∞…£¨“‚Àº“‚Àº£¨±¬Ú∂ý£¨µ¢ŒÛ∏…’˝ ¬£° °™°™°™°™°™°™°™°™°™°™°™°™°™°™°™°™°™°™°™°™ ’‚∂º”– µ¿˝£¨‘ÁƒÍ÷–—ÎæÕ∫≈’ŸÀµ£¨Œ“√«∏˙√¿π˙πÿœµΩÙ’≈£¨√¿π˙µƒ∂´Œ˜“™…˜”√£¨≤ªƒÐ»√◊‘º∫µƒ√¸¬ˆ◊•‘⁄“ª÷⁄√¿π˙∆Û“µ ÷¿Ô£¨“™÷ß≥÷π˙≤˙£¨”»∆‰ «ƒ„√«’‚–©∏þ–≈œ¢ªØ∆Û“µ£¨“™∞⁄Õ—∂‘IOEµƒ“¿¿µ°£ ’‚IOE÷∏µƒ «√¿π˙»˝º“÷¯√˚π´À棨∑÷± «IBM°¢Oracle£®º◊π«Œƒ£©°¢EMC£®“◊∞≤–≈£¨œ÷‘⁄“—æ≠±ª¥˜∂˚≤¢π∫¡À£©£¨÷˜”™“µŒÒ∑÷± «º∆À„°¢ ˝æðø‚°¢¥Ê¥¢£¨À˚√«µƒ≤˙∆∑ø…ŒΩ «Œ“π˙–≈œ¢÷ß÷˘µƒ∞α⁄Ω≠…Ω°£ ÷–—Î∫∞¡À’‚√¥∂ýƒÍ°∞»•IOE°±£¨”––ßπ˚¬£ø∂ý…Ÿ”–“ªµ„°£’Ê»•¡À¬£ø√ª”–£°÷§»Ø°¢“¯––°¢±£œ’°¢ΩªÕ®‘À ‰µ»µ»ªπ «”√µƒ’‚–©∂´Œ˜°£ ±˘∂≥»˝≥þ∑«“ª»’÷Æ∫Æ£¨œÎΩ‚∂≥£¨œÎ·»∆£¨¬˝¬˝¿¥∞…°£ |

|

”–∏ˆ«∞À’÷𖶪∞°£ ƒ„÷ß≥÷π˙≤˙≤Ÿ◊˜œµÕ≥¬£ø ±ÿ–Î÷ß≥÷£° ƒ„÷ß≥÷π˙≤˙CPU¬£ø µ±»ª÷ß≥÷£° ƒ„÷ß≥÷ª™Œ™∫Ë√…¬£ø ◊™Ã»˝∞Ÿ¡˘ Æ∂»÷ß≥÷£° ƒ„‘∏“‚∞Ïπ´”√¡˙–æµÁƒ‘¬£ø ≤ª‘∏“‚£° Œ™ ≤√¥ƒÿ£ø “ÚŒ™’ʵƒ¬Úµ√µΩ°£ |

|

|

|

|

|

’‚√¥Àµ∞…£¨æÕ «¡˙–æ–‘ƒÐôµÕ£¨ŒÞ∑®¬˙◊„ª˘±æµƒ°∞∞Ïπ´–Ë«Û°±£¨æÕ’‚√¥ºÚµ•°£ ¡˙–浃»¥ø…“‘”√¿¥∞Ïπ´£¨’‚ «√ªŒ µƒ£¨µ´ «∞Ïπ´–Ë«Û≤ªΩˆΩˆ «ºÚµ•µƒ∞Ïπ´°£ ≥˝¡À…Ÿ ˝∆Û“µ∫Õ≤ø√≈£¨¥Û≤ø∑÷µƒ∞Ïπ´»À‘±µƒµÁƒ‘£¨Õ˘Õ˘≤ªª·ΩˆΩˆ «”√“ª∞„µƒ∞Ïπ´»Ìº˛°£À˚√«“≤ª·∞≤◊∞∏˜÷÷£¨≤ªæ≠≥£”√ªÚ’þæ≠≥£”√µƒ¥Û»Ìº˛£¨∏¸±Àµ∫Ð∂ý∆Û“µµƒ‘±π§‘ı√¥ø…ƒÐ…œ∞ýæÕ◊®–ƒ∞Ïπ´ƒÿ£ø≤ª“™–𜖔ȿ÷√¥£ø’ʵƒæÕ”√”√excelµƒ µ‘⁄ô…Ÿ¡À°£ ’‚“ªµ„∂º…˺∆»Ìº˛…˙裨∫Õ”≤º˛–‘ƒÐ°£ »Ìº˛ƒ„ø…“‘’“µΩÃÊ¥˙∑Ω∞∏£¨µ´ «÷’æø“™»√»À»• ”¶°£∂¯¥Û≤ø∑÷»À «æÐæ¯∏ƒ±‰µƒ£¨æÕ¡¨∫Ð∂ý»À∞—xpªªwin7 win7ªªwin10∂º≤ªø™–ƒƒÿ°£ Õ‚º”æÕ «”≤º˛–‘ƒÐ≤ª◊„°£ À˘“‘“ª∏ˆ «“™¥Ó‘ÿ÷˜¡˜œµÕ≥£¨“ª∏ˆ «Ã·…˝–‘ƒÐ£¨’‚–©ª·¬˝¬˝∏ƒ±‰£¨µ´ «ƒø«∞ªπ «∆øæ±£¨’‚∏ˆ≤ª «π˙º“Õ∆π„”Î∑ÒƒÐ∏ƒ±‰µƒ£¨’‚ « –≥°–Ë«Ûæˆ∂®µƒ°£ |

|

Œ“π˙Õ∆π„∫Ë√…£∫ ª™Œ™£∫Œ“√«∑¢≤º¡À¥Ó‘ÿ∫Ë√…1.0œµÕ≥µƒ»Ÿ“´÷«ª€∆¡£¨»´√ʺʻðAndroid TVµƒ∏˜÷÷”¶”√£¨ƒ⁄÷√ADB£° Õ¯”—A£∫∑–Ã⁄¡À£°ª™Œ™¥Ú∆∆√¿π˙¬¢∂œ£¨√≥“◊’Ω÷∆≤√œ¬À˘”–πÿº¸≤øº˛±ÿ–Îπ˙≤˙£° Õ¯”—B£∫∫Ë√…÷ß≥÷µƒ”¶”√‘Ÿ…ŸŒ““≤“™¬Ú∫Ë√…£¨≥ı∆⁄µƒ∫Ë√…øœ∂® «≤ªÕÍ√¿µƒ£¨“ÚŒ™∫Ë√… «≤ªÕÍ√¿µƒ’Ω ø£¨∞≤◊ø «ÕÍ√¿µƒ≤‘”¨£¨ƒƒ≈¬≤ª÷ß≥÷º∏∏ˆ”¶”√Œ““≤“™ª®«Æ÷ß≥÷“ªœ¬£¨÷–ª™”–Œ™£° -- Œ“π˙Õ∆π„¡˙–æ£∫ ¡˙–æ£∫«Û«Û¥Ûº“”√”√∞…£¨“—æ≠∏œ…œ¡Ài3µƒ–‘ƒÐ¡À£¨µ±Ã® Ωª˙“—æ≠√ª…∂Œ ¡À£¨‰Ø¿¿∆˜“—æ≠”–¡À£¨Office“≤”–¡À£¨≥£”√»Ìº˛∂º”–÷–ŒƒÃÊ¥˙√‚∑—∞Ê¡À°£ Õ¯”—A£∫’‚√¥¿√µƒ–‘ƒÐ£¨ƒ„∆æ…∂»√Œ“”√£ø Õ¯”—B£∫Œ™…∂÷ªƒÐ≈ÐLinux£øŒ“≤ª∞Æ”√Linux£¨∫Œøˆ¡¨QQ∫ÕŒ¢»Ìoffice∂º√ª”–£¨ƒ„ªπ∫√“‚Àº»√Œ“”√£ø |

|

Õ∆π„√ªŒ £¨µ´ «±œÒƒ≥–©≥ß◊”∞ÛºÐ∞Æπ˙«Èª≥£¨ƒÐ”√MIPSµƒ”√ªß∂º≤ª «–°∞◊£¨±”√ƒ«1000∂ýµƒ∞Â◊”≈‰µ„¿¨ª¯≈‰º˛£¨…œ¿¥æÕ8000ªÚ10000µƒÕÊ°£ Linux√ªŒ £¨≤ªπ˝ªπ «œÎ”√OpenBSD°£¡˙–æ◊‘º∫º”»Î¡À“ª–©Ãÿ∂®÷∏¡ÓºØ£¨≤¢∑«MIPS64±Í◊º÷∏¡ÓºØ£¨±ý“Î∆˜∏¸–¬À∆∫ı√ª∏˙…œΩ¯∂»°£À˘“‘OpenBSD‘⁄ƒ≥∏ˆÃÿ∂®∞ʱæ÷Æ∫Û£¨æÕ√ª–¬µƒCPU÷ß≥÷¡À°£ ∏¸–¬œ¬£∫ RISC-V≥ˆ¿¥¡À£¨MIPS—π¡¶“≤∫Ð¥Û°£ ‘⁄IoT –≥°…œ£¨RISC-V + BSDº“◊µƒ≤˙∆∑£¨ÕÍ»´ø…“‘…Óµ±’‘¥µƒÕʅÓµ –≥°£¨π˙º …œ“≤Àµµƒπ˝»•°£ ¿˚“Êœýπÿ£∫Fullstack CRUD boy |

|

œ˚∑—’þ≤¢≤ª π”√”≤º˛£¨œ˚∑—’þ π”√µƒ «app°£ appø™∑¢’þ“≤≤ª π”√”≤º˛£¨appø™∑¢’þ π”√µƒ «≤Ÿ◊˜œµÕ≥£®Ã·π©µƒapi£©Ω¯––±ý≥ð£ ≤Ÿ◊˜œµÕ≥≤≈ «÷±Ω” π”√”≤º˛µƒ“ª∑Ω°£µ´£¨”–√ª”–Œ™¡˙–æø™∑¢µƒ≤Ÿ◊˜œµÕ≥£ø”–£¨µ´≤¢≤ª¡˜––°£ À˘“‘£¨’˚∏ˆππºÐ «£∫œ˚∑—’þ π”√app£¨appø™∑¢’þ π”√≤Ÿ◊˜œµÕ≥£¨≤Ÿ◊˜œµÕ≥ π”√”≤º˛°£ ƒ„÷ªÕ∆π„π˙≤˙”≤º˛£¨≤ªÕ∆π„÷ß≥÷’‚∏ˆ”≤º˛µƒ≤Ÿ◊˜œµÕ≥£¨ƒ«”– ≤√¥”√ƒÿ£ø ø…ƒÐ”–»Àæıµ√ƒ≥ƒ≥ «π˙≤˙≤Ÿ◊˜œµÕ≥£¨µ´ «ƒ≥ƒ≥π˙≤˙≤Ÿ◊˜œµÕ≥£¨À¸£®÷¡…Ÿƒø«∞£©≤¢≤ª÷ß≥÷¡˙–æ°£ “Ú¥À£¨Õ∆π„¡˙–棨 «“ª’˚Ãı≤˙“µ¡¥£¨≥˝¡ÀÕ∆π„”≤º˛£¨ªπµ√Õ∆π„¡˙–æœýπÿ≤Ÿ◊˜œµÕ≥£¨ªπµ√»√ø™∑¢’þŒ™œýπÿ≤Ÿ◊˜œµÕ≥ø™∑¢»Ìº˛°£°£°£ ’‚“ªœµ¡–µƒπ§◊˜£¨»´∂º”…π˙º“¿¥◊ˆµƒª∞£¨∫Ѓ—◊ˆµΩ°£Œ“œý–≈π˙º“œÎªπ «œÎµƒ£¨µ´∏˘±æ√ª”–◊„𪵃Õ∂»Î∏˙‘§À„¿¥◊ˆ’‚º˛ ¬°£ ƒ≥ÀΩ»À∆Û“µªÚ–̃Ð◊ˆµΩ’‚—˘µƒÕ∆π„ƒÐ¡¶∏˙÷¥––¡¶£¨µ´»Àº“”÷≤ªƒÒ¡˙–棨‘ı√¥∞σÿ£ø |

|

’‚∏ˆŒ ”¶∏√Œ √¥£ø’‚√¥∂ýπ˙≤˙CPUŒ™ ≤√¥‘⁄÷™∫ı…œ£¨æÕ¡˙–擪÷±‘⁄Œ £¨Œ™…∂≤ª÷ß≥÷Œ“£ø –≥°æ≠º√£¨”√ªß◊‘”…—°‘Ò£¨ªπ“ÚŒ™…∂£ø”¶∏√Œ µƒ «Œ™…∂√ª”–±µƒCPU¿¥¬Ù≤“£ø’◊–收∏√Œ £¨Œ™…∂≥˝¡À…œ∫££¨∂º≤ª¥˝º˚À˚£ø≤ø∑÷‘≠“Ú «¡˙–æ∞—’◊–æ≈Á≥…¬Ú∞Ï¡À∞…°£ª™Œ™µƒˆÔ≈Ù«ø∞…£¨Œ™…∂≤ªƒÐŒ Œ £¨Œ™…∂¿œ√¿æÕ πæ¢÷∆≤√À˚£¨‘≠“Ú «À˚«ø∞°£°ªπ”–∫£π‚°¢∑…Ã⁄∫Õ…ÍÕ˛£¨∂º…œ÷∆≤√√˚µ•¡À£¨“ÚŒ™À¸√«’ʵƒø…“‘◊ˆ∏þ–‘ƒÐº∆À„£°¡˙–æ «≤ª «”¶∏√‘⁄Œ œ˙¡ø÷Æ«∞œ»Œ Œ ◊‘º∫£¨Œ™…∂–˚¥´◊Ó◊‘÷˜µƒ◊‘º∫£¨Ω¯≤ª¡À√¿Dµƒ∑®—€∞°£ø ÀµµΩµ◊£¨ªπ «≤˙∆∑≤ª––£¨πÛ£¨…˙è≤Ó£¨◊Ó“™√¸≤ªŒ»∂®°£À¸–˚¥´◊Ó∆梵ƒ «÷∏¡ÓºØ£¨∆‰ µ≤ª «”√ªß∫Õπ˙º“µƒÕ¥µ„£¨π˙ƒ⁄ ≤√¥÷∏¡ÓºØ∂º”–£¨‘⁄’‚µ„…œ¿œ√¿∏˘±æø®≤ª◊°°£∆‰À¸∑Ω√Ê∂º±»±»À≤Ó£¨∞¸¿®Œ¢ºÐπ𣨱»À”√∏¸–°µƒ√ʪ˝π¶∫ƒ£¨ƒÐ◊ˆ≥ˆ∏¸Œ»∂®–‘ƒÐ≤Ó≤ª∂ýªÚ∏¸∫√µƒ∫À£¨À¸“ª÷±π•ª˜µƒ∑…Ã⁄’◊–æ∫Õ∫£Àº£¨’‚–©∂º «◊‘º∫◊ˆCPU∫Àµƒ°£ À¸∆≤Ω‘Á£¨¥”÷–ø∆‘∫≥ˆ¿¥£¨◊‘»œŒ™π˙º“”¶∏√÷ß≥÷À¸£¨µ´œ÷‘⁄◊˜Œ™∑Ú∆ÞµÍ√Ò”™∆Û“µ£¨”¶∏√µ˜’˚–ƒÃ¨£¨ƒÐ¡¶≤ª––◊ˆµ„±þ±þΩ«Ω«æÕ∫√¡À£¨ƒÐ¡¶«øæÕ»•’˘£¨≈еΩ÷™∫ı◊‘Œ ◊‘¥¬Ù≤“À„∏…¬ÔµŒ£¨20ƒÍ“—æ≠’¥¡À÷–ø∆‘∫≤ª…Ÿπ‚£¨∫˙¿œ∞“≤≥…¡Àπ˙ƒ⁄xc◊Ó”–«Æµƒ¿œ∞£¨ªπœÎ∏……∂£¨√ª”–»ÀœÒ¡™œÎ“ª—˘£¨◊∑æø‘≠◊ÔæÕ≤ª¥Ì¡À£¨¬Úº∆À„À˘µƒ÷™ ∂≤˙»®º€∏Ò «À≠∂®µƒ£øπ˙º“…∂ ±∫Ú∑≈∆˙∆Û“µøÿ÷∆»®µƒ£ø “ÚŒ™¡˙–æ‘⁄π˙≤˙CPU÷–≤¢≤ªÕª≥ˆ£¨∞¸¿®∆‰¬Ù¡¶–˚¥´µƒ◊‘÷˜ø…øÿ°£ |

|

œ÷‘⁄√ª”–◊®√≈Õ∆π„¡˙–棨º∏∏ˆ–≈¥¥cpu∏˜◊‘ø™Õÿ –≥°°£œ÷‘⁄ªπ «ª™Œ™”Î∫£π‚£®amd£©œý∂‘◊ˆµƒ∫√“ª–©°£“ÚŒ™ª™Œ™ƒ⁄≤ø…˙è∫√£¨amd ≈‰–‘∫√°£ ¡˙–浃µ¿¬∑±æ…Ì“™ƒ—“ªµ„£¨∆Ωµÿ∆∏þ¬•£¨’Ê’˝‘⁄°∞‘Ϻ∆À„ª˙°±£¨∂¯«“¥Í≥ˆ¡Àπ˙ƒ⁄µ•∫À◊Ó«øµƒcpu£®ª˘◊º≤‚ ‘¬‘∏þ”⁄9000s£¨kx7000gƒø«∞√ª”–ø… €≤˙∆∑£¨–‘ƒÐ≤ªø…÷™£¨amdµƒ≤ªƒÐÀ„£©£¨À≥¥¯◊ˆ¡À“ª≈˙÷––°cpu £¨∂˛¥Œø™∑¢º∏∏ˆ≤Ÿ◊˜œµÕ≥£¨◊ˆ¡À“ª≈˙±ý“Î∆˜£¨–ȃ‚ª˙£¨◊ˆ¡À‰Ø¿¿∆˜£¨◊ˆ¡À”¶”√»Ìº˛£¨º∏∞Ÿ»Àµƒπʃ££¨◊ˆ’‚√¥∂ý ¬«È£¨ªπ «≤ª»ð“◊°£œ£Õ˚¡˙–æƒÐ’ıµΩ“ª–©«Æ£¨¥Í≥ˆ∏¸∫√µƒcpu°£ |

|

˜Ë˜ÎˆÔ≈Ù“—æ≠µ√µΩ¡À√¿π˙…ÃŒÒ≤øµƒ»œø…£¨ΩÒÃÏ∑…Ã⁄…ÒÕ˛“≤µ√µΩ¡À√¿π˙…ÃŒÒ≤øµƒ»œø…°£ ªÚ’þÀµ¥ÛΩƌ޻Àª˙∂ºƒÐªÒµ√»œø…£¨µ´»‘»ªæý¿Î¡˙–æªπ”–∫√‘∂µƒ∏–æı°£ |

|

–∂—¸°≠°≠ “ÚŒ™æÕ√ª”–ƒÐ”√µƒ√Ò”√≤˙∆∑°£∂¯«“≥˝∑«»´∂ºªª¡À≤ª»ªøÁ∆Ωî∫е∞Àµƒ£¨÷∏¡ÓºØ∂º≤ª“ª—˘ |

|

1.¡˙–æ≤ª «X86ºÐπ𣨔√≤ª¡ÀWindows°£ 2.¡˙–æ≤ª «ARMºÐππ£¨¡¨”√∞≤◊ø∂ºµ√≤ªµΩ∫Ð∫√÷ß≥÷°£¡˙–æ «MIPS°£ À˘“‘ƒ„“™‘⁄∆’Õ®”√Õæ…œÕ∆π„ «“©Õ˵ƒ°£“ª∏ˆ ≤√¥÷˜¡˜œµÕ≥∂º”√≤ª¡ÀµƒÕÊ“‚ƒÐ”– –≥°£ø ÷ª≤ªπ˝¡˙–æÀ‰»ª≤ª◊ˆ∆’Õ®√Ò”√¡Ï”Ú£¨µ´ƒÐ◊ˆ◊®“µæ¸π§¡Ï”Ú°£ ±»»ÁDSP–æ∆¨µƒIP∫À |

|

Àµƒ«–©”–µƒ√ªµƒ∂º√ª”–”√£¨Õº∞…¿¨ª¯¿–“ª≤‚æÕ÷™µ¿ ”∆µ£∫°æÕº∞…‘”Ã∏°ø¡˙–滶√ª”–◊ ∏Ò∂®“Â’◊–æ «∑Òº∑—¿∏ý£¨’◊–æ6ƒÍ–‘ƒÐ÷…˝7±∂¥ÔµΩ7¥˙I5ÀÆ∆Ω BV1W14y127FB ‘≠ ”∆µ£∫”¢Ãÿ∂˚Õ¥ ß—¿∏ý≥ß√˚£¨—¿∏ýÕıŒ©ƒ˙’◊–æ∂¿◊ BV1v84y1q7d7 gueenet°§ 2022-10-21 £®¡˙–æ∞…–°∞…÷˜£© ¥À»À±ªÕº∞…¿¨ª¯¿–µƒ∂ýœÓ≤‚ ‘¥Ú¡≥£¨ƒø«∞“—∆∆∑¿∞—‘€¿≠∫⁄£¨‘€»¥¥” º÷¡÷’≤¢√ª”–¿≠∫⁄’‚Œª¡˙–æ∞…–°∞…÷˜ ±æ∆™Œ™ ”∆µ± º«¥Êµµ£¨≤¢√ª”–ô∂ýµƒ¬€÷§ °¡˜£∫ |

|

|

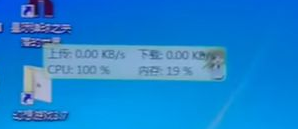

’‚ « ƃͫ∞µƒ’◊–æAÀ´∫À∞ÂU£¨¿¨ª¯¿–”⁄2023ƒÍ≥ı“‘48Ω≠’„ª¶∞¸” µƒº€∏Òπ∫»Î£¨–Õ∫≈C4350AL |

|

|

|

|

|

ø™ª˙CPUª·’º”√100%∫Ð≥§ ±º‰ŒÞ∑®∂ØµØ ª∫“ªª·∂˘≤≈ƒÐ∫√ |

|

|

|

|

|

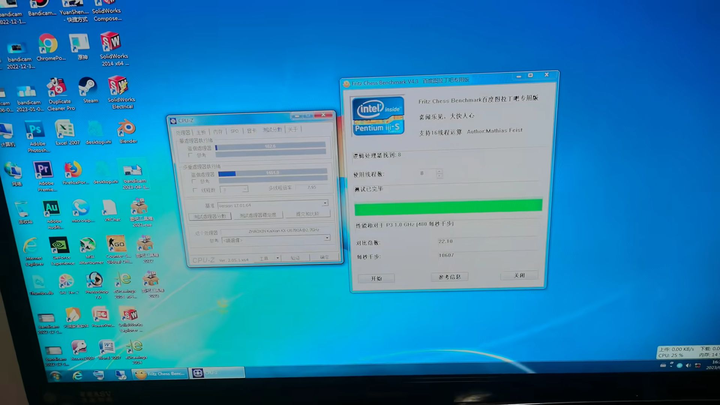

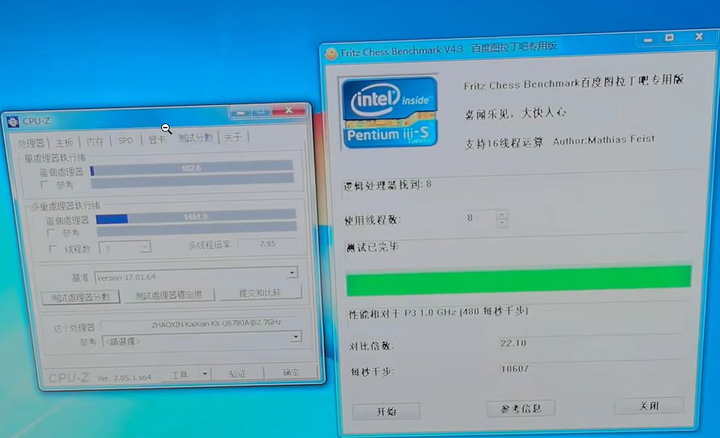

œÛ∆Â≈Ð∑÷÷ª”–3±∂∂ý£¨CPUz≈Ð∑÷200≥ˆÕ∑ |

|

|

19ƒÍµƒKX6000£®’◊–æE£©∞À∫À∞ÂU£¨’˚ª˙”⁄2022ƒÍµ◊550∞¸” π∫»Î£¨»ÁΩÒ“—æ≠450∞¸” £¨CPU–Õ∫≈KX-U6780A |

|

|

|

|

|

œÛ∆Â≈Ð∑÷≥¨π˝22±∂£¨CPUz≥¨π˝1400∑÷ |

|

|

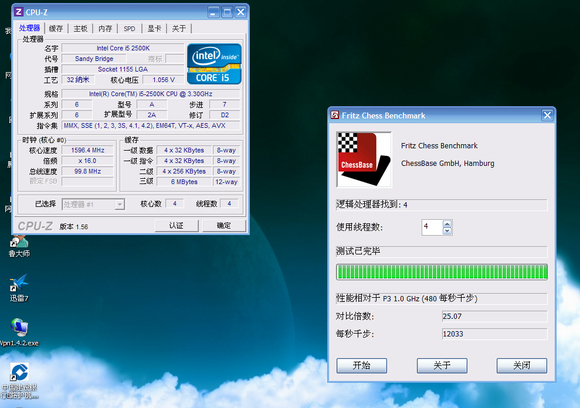

Õº∞…µƒI5 2500K≈Ð∑÷,ø…“‘ø¥µΩœÛ∆Â≈Ð∑÷25.07 12033£®4.0G£© |

|

|

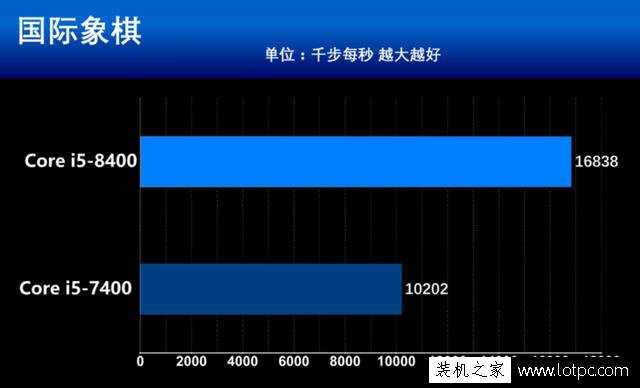

17ƒÍµƒI5 7400”Î8400≈Ð∑÷∂‘±»£¨ø…“‘ø¥µΩI5 7400 œÛ∆Â10202£¨’‚≈Ð∑÷∑¥µπœ¬Ωµ¡À¡˘∑÷÷Æ“ª£¨”¢Ãÿ∂˚º∑¡À’‚√¥∂ýƒÍµƒ—¿∏ý∫¶Àıªÿ»•¡À I5 7400 17ƒÍ∑¢≤º£¨ €º€$182.00 I5 2500K 11ƒÍ∑¢≤º£¨ €º€1400RMB£¨19ƒÍ €º€170 ∑≠“Î∑≠“Σ¨¡˙–æ∞…–°∞…÷˜Àµ’◊–æº∑—¿∏ý ≤√¥Ω–’Ê’˝µƒº∑—¿∏ý£ø’‚?≤≈Ω–’Ê’˝µƒº∑—¿∏ý °™°™µ±ƒÍ‘€◊Ðæıµ√¬Þ”¿∫∆¿œ¥Ú∂œÕı◊‘»Áœ‘µ√∫Ð√ª¿Ò√≤£¨œ÷‘⁄ªÿÕ∑ø¥¿œ¬Þ√ªµ±≥°’Ê»ÀøÏ¥Úœ÷≥°PK «¿œ¬Þ’Ê”–∫≠—¯°£ æÕ’‚–© |

|

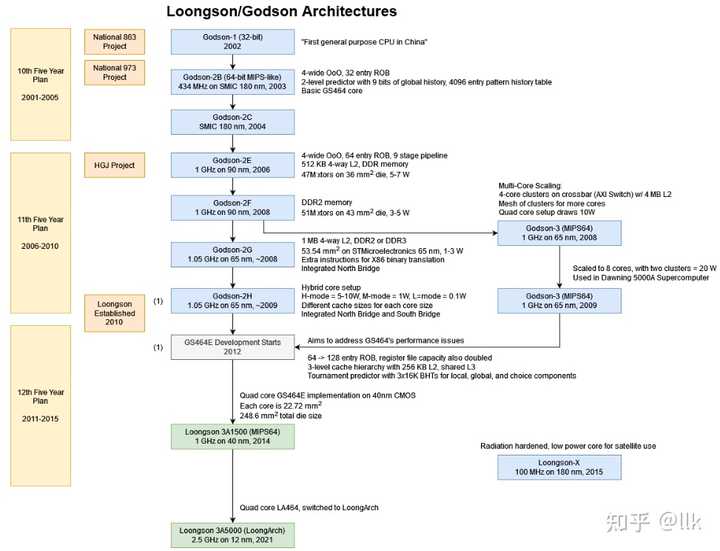

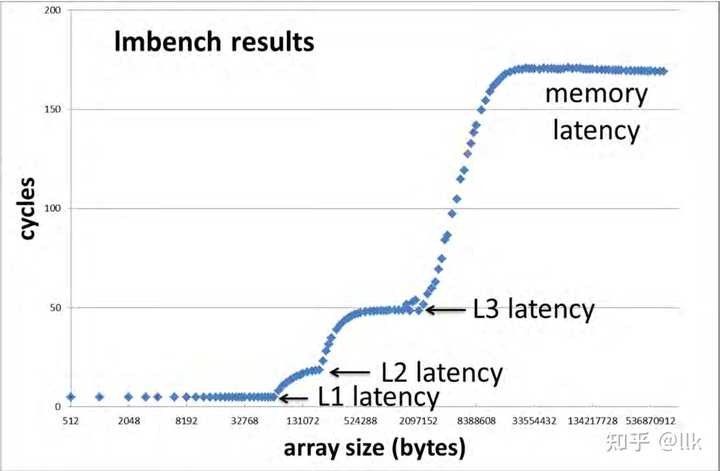

Ω·¬€ «“—æ≠ª®¡À∫Ð∂ýæ´¡¶£¨µ´ « –≥°ª·◊‘º∫◊ˆ≥ˆ—°‘Ò°£≥˝¡À…Óµ…œµƒ‘≠“Ú£¨Ω®“ÈÂ÷˜ø¥ø¥Œ“µƒ¡˙–æ∑¢’π¿˙ ∑Œƒ’¬£¨ø…“‘¥”ºº ıΩ«∂»µ√µΩ“ª–©¥∞∏°£ «∞—‘ ◊ÓΩ¸º∏ƒÍœµÕ≥–‘µƒ—ßœ∞≤¢ ·¿Ì¡ÀΩ¸30∂ýƒÍµƒº∆À„ºº ı∑¢’π¿˙ ∑£¨…‘”–∏–ŒÚ°£ÀÏæˆ∂®Ω´÷Æ’˚¿Ì≥…Œƒ£¨ƒøµƒ”–∂˛£¨“ª¿¥◊˜Œ™÷™ ∂≥¡µÌ£¨¥Æ¡™∆≤ªÕ¨ºº ı£¨Õ⁄æÚ≤ªÕ¨ºÐππ÷ƺ‰µƒ‘®‘¥£¨∂˛¿¥Õ®π˝’˚¿Ì‘Ÿ¥Œ…Û ”¿˙ ∑£¨∆⁄Õ˚ø˙º˚Œ¥¿¥∑¢’π∑ΩœÚ°£Œ“Ω´±æœµ¡–√¸√˚Œ™º¯Õ˘÷™‘∂, ÷˜“™πÿ◊¢º∆À„”Ϊ•¡™°£ ±æŒƒŒ™µ⁄∂˛∆™£¨÷˜“™ªÿπÀ¡˙–朵¡–°£ 0. ∏≈ ˆ ¡˙–æ∏˘æðºÐππµƒ≤ªÕ¨£¨¥Ê‘⁄ 3 ∏ˆ¥¶¿Ì∆˜œµ¡–°£ ¡˙–擪∫≈£¨”√”⁄œ˚∑—µÁ◊”∫Õ«∂»Î Ω”¶”√ ¡˙–æ∂˛∫≈£¨”√”⁄«∂»Î Ω”¶”√∫ÕµÕ–‘ƒÐ∏ˆ»Àº∆À„ª˙µƒµ•∫À¥¶¿Ì∆˜ ¡˙–æ»˝∫≈£¨”√”⁄∏¸∏þ–‘ƒÐº∆À„ª˙°¢∏þ–‘ƒÐº∆À„∫Õ∑˛ŒÒ∆˜µƒ∂ý∫À¥¶¿Ì∆˜ ¡˙–楶¿Ì∆˜∫À∞¥’’Œ¢ºÐππ£¨∑÷Œ™Àƒ¿ý£¨∑÷± «£∫ µ•∑¢…‰32Œª£®132£©GS132£∫¥¯”≤º˛∑÷∆µ∆˜µƒª˘±æ«∂»Î Ω MIPS32 ƒ⁄∫À°£3- (GS132) ªÚ 5- (GS132E) º∂¡˜ÀÆœþ À´∑¢…‰32Œª£®232£©GS232£∫∏þ∂À«∂»Î Ω MIPS32 GS232 ◊Ó∂ý”– 5 º∂¡˜ÀÆœþ£¨500MHz£¨16KB L1°£GS232 ÷˜“™”√”⁄¡˙–擪∫≈≤˙∆∑ GS232E◊Ó∂ý”– 10 º∂¡˜ÀÆœþ£¨1000 MHz£¨16KB L1£¨L2 = 4 MB π≤œÌ°£¬“–Ú÷¥–– Àƒ∑¢…‰64Œª£®464£© GS464£∫æþ”–Àƒ¬∑≥¨±Í¡ø¬“–Ú÷¥––µƒMIPS64ƒ⁄∫À°£∏√…˺∆∆‘¥”⁄¡˙–æ2F¥¶¿Ì∆˜ GS464 ÷ß≥÷ MIPS64 R2 + LoongMMI£®2E ∫Õ 2F ÷–µƒ¡Ω∏ˆ≤ªÕ¨∞ʱ棩 GS464V ”⁄ 2010 ƒÍÀÊ¡˙–æ3B ◊¥ŒÕ∆≥ˆ£¨ «æþ”– ∏¡øπ¶ƒÐµƒ GS464GS464E « GS464 µƒ∏ƒΩ¯∞ʱ棨∞¸¿®∏¸¥Ûµƒª∫¥Ê∫Õ∏¸∫√µƒ∑÷÷ß‘§≤‚µ» GS464EV « GS464 œµ¡–µƒ∑¢’𣨠◊œ»±ª 3A4000 ¥¶¿Ì∆˜ π”√ À´∑¢…‰64Œª£®264£©GS264£∫MIPS64 ƒ⁄∫À£¨ «GS232µƒ64Œª µœ÷ ¡ÌÕ‚£¨LA464 « GS464µƒ∑¢’π£¨÷ß≥÷ LoongArch°£œ¬Õº’π æ¡À¡˙–æ∏˜¥˙≤˙∆∑÷ƺ‰ºÃ≥–∫Õ∑¢’ππÿœµÕº£∫ |

|

|

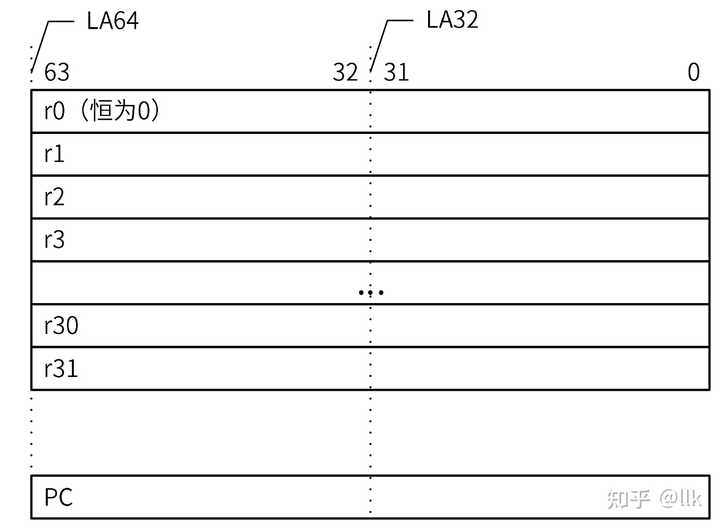

¡˙–æ 1 º¥Godson-1 «µ•∑¢…‰¬“–Ú32Œª¥¶¿Ì∆˜£¨ «÷–π˙π˙ƒ⁄…˺∆µƒµ⁄“ª∏ˆÕ®”√¥¶¿Ì∆˜ ¡˙–æ 2 « MIPS III ºÊ»ð 64 Œª¥¶¿Ì∆˜œµ¡–°£”Ρ˙–æ 3 œµ¡–π≤œÌ GS464¥¶¿Ì∆˜∫À£¨¡˙–æ 2µƒ∑¢’ππ滮 «¥”CPU∑¢’πŒ™SOC°£¡˙–æ 2E (2006) «“ª∏ˆ CPU£¨2F (2007) ºØ≥…¡À±±«≈°£2F µƒ…˺∆ « GS464 ∫À–ƒµƒª˘¥° 2009ƒÍµƒ¡˙–æ 3A1000 «µ⁄“ª∏ˆ…˙≤˙µƒ¥¶¿Ì∆˜£¨ π”√ 4 ∏ˆ GS464 ƒ⁄∫À£¨65 nm𧓒°£ ¡˙–æ 3A1000 ƒÐπª“‘Ω”Ω¸ 1 GHzµƒ ±÷”ÀŸ∂»‘À––£¨ ◊œ» «4 ∏ˆ CPU ƒ⁄∫À£®~15 W£©£¨»ª∫Û « 8 ∏ˆƒ⁄∫À£®40 W£©µƒ¡˙–æ3B1500 2015 ƒÍ£¨∑¢≤º¡À ¡˙–æ3A1500 ∫Õ ¡˙–æ3B2000°£ π”√‘ˆ«ø–Õ GS464E ¥¶¿Ì∆˜∫À£¨∏ƒΩ¯∫ÛµƒŒ¢ÃÂœµΩ·ππ÷π©¡À∏¸∫√µƒ–‘ƒÐ£¨æð±®µ¿ÀŸ∂» « ¡˙–æ3A1000 µƒ 3 ±∂£¨≤¢«“ªπ“˝»Î¡À LoongISA ‘ˆ«ø–Õ÷∏¡ÓºØ°£ ¡˙–æ3A1500 ”√”⁄«∂»Î Ω”¶”√£¨∂¯ ¡˙–æ3B2000 ”√”⁄∑˛ŒÒ∆˜∫Õ PC 2017ƒÍ¡˙–æ∑¢≤º¡˙–æ3A3000°£¡˙–æ3A3000 ≤…”√Àƒ∫À 64 Œª…˺∆£¨÷˜∆µŒ™ 1.5 GHz£¨π¶∫ƒΩˆŒ™ 30 W 2019 ƒÍµ◊£¨∑¢≤º¡À ¡˙–æ3A 4000 ∫Õ ¡˙–æ3B 4000 œµ¡–°£ π”√¡À…˝º∂∫Ûµƒ GS464EV Œ¢ºÐππ°£¥¶¿Ì∆˜…˺∆”–Àƒ∏ˆƒ⁄∫À£¨8MB µƒ L3 ª∫¥Ê∫Õ 1.8 GHz ÷¡ 2 GHz ÷ƺ‰µƒπ§◊˜ ±÷” 2021ƒÍ7‘¬£¨¡˙–æ3 5000œµ¡–∑¢≤º°£∏√œµ¡–¥¶¿Ì∆˜ «¡˙–æ ◊øÓ◊‘÷˜—–∑¢µƒLoongArch÷∏¡ÓºØºÐππ£¨∞¸¿® ¡˙–æ3A5000£¨“ª∏ˆÀƒ∫Àî Ωª˙ CPU ∫Õ 3C5000L£¨“ª∏ˆ Æ¡˘∫À∑˛ŒÒ∆˜ CPU£¨ª˘”⁄µ•∏ˆ∑‚◊∞÷–µƒÀƒ∏ˆ 3A5000°£ π”√LA464¥¶¿Ì∆˜∫À 2023ƒÍ11‘¬£¨¡˙–æπŸ∑Ω∑¢≤º¡˙–æ3A6000 π”√ «6∑¢…‰À´œþ≥õƒLA664¥¶¿Ì∆˜∫À ±æŒƒ÷˜“™πÿ◊¢¡˙–æ»˝∫≈£¨∆‰Œ¢ºÐππ÷˜“™Œ™Àƒ∑¢…‰64Œª£¨º¥GS464œµ¡–°£πÿ”⁄¡˙–æ÷∏¡ÓºØºÐππ¿˙ ∑‘®‘¥«Î≤Œøºµ⁄“ª’¬¡˙–æ÷∏¡ÓºØºÐππµƒΩȅа£±æŒƒÕ®π˝œµÕ≥–‘ªÿπÀ’˚∏ˆ¡˙–朵¡–¥¶¿Ì∆˜£¨ ‘ÕºÕ®π˝¡˙–朵¡–¥¶¿Ì∆˜∑¢’πµƒ¿˙ ∑¬ˆ¬Á£¨¿¥’πœ÷π˙ƒ⁄¥¶¿Ì∆˜ºº ı∑¢’π¿˙≥㨓‘º∞∫Õπ˙º ÷˜¡˜¥¶¿Ì∆˜≥߅õƒ≤Ó“Ï°£œ¬±Ì◊ÐΩ·¡À∏˜¥˙¥¶¿Ì∆˜÷ƺ‰µƒπÿº¸÷∏±Í∫ÕπÊ∏Ò£∫ Godson-1Godson-2BGodson-2CGodson-2ELoongson 2FLoongson 2GLoongson 3A1000Loongson 3B1500Loongson 3A2000Loongson 3A3000Loongson 3A4000Loongson 3A5000Loongson 3A6000Date2001200320042006200820102009201520152016201920212023Core NameGS132NANAGS464r1GS464r1GS464r2GS464r2GS464VGS464EGS464EGS464EVGS464V/LA464LA664Technology0.18um0.18um0.18um90nmST 90nmST 65nmST 65nmSMIC 32nmSMIC 40nmST 28nmST 28nm12nm12nmTransistors4M15M15M47M51M100M425M1.14B8B8BArea(mm^2)NA41.541.5364354140182.5248.6(17.66x14.08)248.6(25.3x28.8)232147TDP(W)0.5NANA5-73-531530-6015405035Frequency(GHz)0.2660.250.4510.810.8-11.50.8-11.2-1.51.82.3-2.52.5No. Inst Decode1444444444444No. Inst Issue1444444444446COREs1111114844444ThreadsSTSTSTSTSTSTSTSTSTSTSTSTSMT2L1 CacheI$: 8K 2 way D$: 8K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayI$: 64K 4 way D$: 64K 4 wayL2 CacheNA8MB offchip8MB offchip512K 4 way512K 4 way1M 4 way4M 8 way128K/Core256K/Core 16 way256K/Core256K/Core256K/Core 16 way256K/CoreL3 CacheNANANANANANANA8M4M 16 way8M 16 way8M 16 way16M 16 way16M 16 wayIOPCIPCIPCIPCIPCIPCIHT 1.0 2x8@800MHzHT 2.0 2x16@3.2GHzHT 2x16@3.2GHzHT 2x16@3.2GHzHT 2x16@3.2GHzHT 2x16@3.2GHzHT 3.0 x16@6.4GHzMemory8-256M128bit 64M-2GDDRDDR2DDR2-333DDR2/3DDR2/3DDR2-800/3-1200 2x72DDR2-800/3-1333 2x72DDR2-800/3-1600 2x72DDR4-2400 2x72DDR4-3200 2x72DDR4-3200 2x72@42GB/sCommentsMIPS-III 32MIPS-III 64MIPS-III 64MIPS-III 64MIPS-III 64MIPS64MIPS64LoongISA 1.0LoongISA 1.0LoongISA 1.0LoongISA 2.0LoongISA 2.0 ø…“‘∑¢œ÷£¨¡˙–楶¿Ì∆˜∫Ð∂ýæ´¡¶∂ºª®‘⁄÷∏¡ÓºØ…œ¡À£¨∂¯±æ…Ì¥¶¿Ì∆˜∫ÀµƒŒ¢ºÐππ∏¸–¬±»Ωœª∫¬˝°£ ±æŒƒ◊È÷Ø–Œ Ω»Áœ¬: µ⁄“ª’¬ºÚµ•ΩȅС˙–æ÷∏¡ÓºØºÐππLoongArch v1.02 µ⁄∂˛’¬ΩÈ…ÐGodson-1µƒŒ¢ºÐππ£¨¡ÀΩ‚¡˙–æƒÀ÷¡÷–π˙µƒµ⁄“ª∏ˆ¥¶¿Ì∆˜…˺∆ µ⁄»˝’¬ΩÈ…ÐGodson-2∫ÕGodson-3Aµƒ¥¶¿Ì∆˜∫ÀGS464Œ¢ºÐππ£¨∫Û–¯¡˙–æ∂º «“‘GS464Œ™ª˘¥° µ⁄Àƒ’¬ºÚµ•√Ë ˆLoongson-3B1500 ’˚úÐππ“‘º∞÷ß≥÷œÚ¡ø‘ÀÀ„µƒ¥¶¿Ì∆˜∫ÀGS464VŒ¢ºÐππ µ⁄ŒÂ’¬ΩÈ…ÐLoongson-3A2000µƒ¥¶¿Ì∆˜∫ÀGS464EµƒŒ¢ºÐππ µ⁄¡˘’¬ºÚµ•ΩȅЪ˘”⁄GS464EµƒLoongson-3A3000£¨÷˜“™ «ª˘”⁄Loongson-3A2000◊ˆ¡À𧓒…˝º∂ µ⁄∆þ’¬ºÚµ•ΩȅЪ˘”⁄GS464EVµƒLoongson-3A4000£¨ µ⁄∞À’¬ΩȅЪ˘”⁄LA464¥¶¿Ì∆˜∫ÀµƒLoongson-3A5000 µ⁄æ≈’¬ΩÈ…ÐLoongson-3A6000Œƒ’¬◊Ó∫Û¡–≥ˆ¡À÷˜“™µƒ≤ŒøºŒƒœ◊1. LoongArch÷∏¡ÓºØºÐππ ¡˙–浃÷∏¡ÓºØºÐππ∑÷Œ™»˝∏ˆΩ◊∂Œ£∫ MIPS ¡˙–æ‘⁄≥ı ºΩ◊∂Œ π”√MIPS64 ÷∏¡ÓºØºÐππ(ISA)°£2009 ƒÍ 6 ‘¬£¨ICT ÷±Ω”¥”MIPSπ´ÀæªÒµ√¡À MIPS32 ∫Õ MIPS64 ºÐπ𵃖Ìø…°£2011 ƒÍ 8 ‘¬£¨¡˙–æø∆ºº”–œÞπ´À楔 MIPS π´ÀæªÒµ√ MIPS32 ∫Õ MIPS64 ºÐππ–Ìø…£¨”√”⁄ºÃ–¯ø™∑¢ª˘”⁄ MIPS µƒ¡˙–æ CPU ƒ⁄∫À LoongISA 2015ƒÍ¡˙–æ3A2000≤…”√LoongISA 1.0¿©’π÷∏¡ÓºØ£¨ « MIPS64 µƒ≥¨ºØ°£LoongISA ÷∏¡Ó◊˜Œ™ GS464E ƒ⁄∫Àµƒ“ª≤ø∑÷“˝»Î°£∞¸¿®œ¬¡–≤ø∑÷£∫ LoongEXT£¨Õ®”√¿©’π£¨148 Ãı÷∏¡Ó LoongVZ£¨MIPS64 ∞ʱæ 5 ÷–“˝»Îµƒ°∞VZ°±œµÕ≥µƒ–ȃ‚ªØ¿©’π£¨5 Ãı÷∏¡Ó LoongBT£¨∏¸øϵƒ x86 ∫ÕARM∂˛Ω¯÷∆∑≠“Σ¨213 Ãı÷∏¡Ó LoongSIMD£¨‘≠√˚LoongMMI£®‘⁄¡˙–æ2E/F£©£¨Œ™128ŒªSIMD£¨1014Ãı÷∏¡Ó ¿¥◊‘ MIPS µ⁄ 5 ∞ʵƒ MIPS SIMD ºÐππ (MSA)°¢DSP ∫Õ VZ ƒ£øÈLoongArch ÀÊ◊≈¡˙–æ 3 5000 œµ¡–µƒ∑¢≤º£¨¡˙–æ‘⁄ 2021 ƒÍ◊™œÚ¡À◊‘º∫µƒ¥¶¿Ì∆˜÷∏¡ÓºØºÐππ(ISA)°£LoongArch ∞¸¿®“ª∏ˆºÚªØµƒ 32 Œª∞ʱ森LA32R£©£¨“ª∏ˆ±Í◊ºµƒ 32Œª∞ʱæ (LA32S) ∫Õ 64 Œª∞ʱæ (LA64)°£ LoongArch ISA ÷≤·“—”⁄ 2021 ƒÍ 8 ‘¬≤ø∑÷ø…”√£¨∆‰µ⁄“ªæ̺«¬º¡Àª˘±æºÐππ°£∏˘æðLoongArch ÷≤·£¨ISA π”√¡ÀMIPSµƒÃÿ»®ƒ£–Õ∫ÕIRQª˙÷∆£¨∆‰À˚≤ø∑÷¥Û∂ý◊Ò—≠RISC-Vµƒ◊ˆ∑®£∫»•µÙ¡À∑÷÷ß—”≥Ÿ≤€£¨∏ƒ±‰¡À÷∏¡Ó±ý¬Î°£LoongArch «»´–¬µƒ÷∏¡ÓºØ£¨≤ª «‘⁄ MIPS …œ◊ˆµƒ¿©’π°£∞¸∫¨ª˘¥°÷∏¡Ó 337 Ãı°¢–ȃ‚ª˙¿©’π 10Ãı °¢∂˛Ω¯÷∆∑≠“ο©’π176 Ãı°¢128 ŒªœÚ¡ø¿©’π 1024 Ãı°¢256 ŒªœÚ¡ø¿©’π 1018 Ãı£¨π≤º∆ 2565 Ãı‘≠…˙÷∏¡Ó°£œý∂‘”⁄MIPS£¨Þ∆˙¡À≤ø∑÷≤ª ∫œœ÷¥˙CPUµƒ÷∏¡Ó£¨”÷◊ˆ¡À¥Û¡ø∏ƒΩ¯∫Õ¿©’π°£¿˝»Áµ•Ãı÷∏¡Ó÷ß≥÷µƒ¡¢º¥ ˝¥”MIPSµƒ◊Ó¥Û16Œª¿©’πµΩ◊Ó¥Û24Œª£¨∑÷÷ßï◊™∆´“∆“≤¥”64K¿©’πµΩ1M◊÷Ω⁄£¨“‘º∞—∞÷∑ø’º‰¥”πÃ∂®∑÷∂Œ∏ƒ±‰Œ™µ•“ª∆Ω√ʵ»£¨∂º”––ߺı…Ÿ¡À±ý“ÎΩ·π˚µƒƒø±Í÷∏¡ÓÃı ˝∫Õ∑√¥Ê¥Œ ˝£¨Ã·∏þ¡À–߃а£LoongArchµƒ÷∏¡ÓœµÕ≥‘⁄…˺∆ ±£¨“‘œ»Ω¯–‘°¢¿©’π–‘°¢ºÊ»ð–‘Œ™ƒø±Í£¨∆‰÷–ºÊ»ð–‘ «÷∏»⁄∫œMIPS/x86/ARM÷∏¡ÓœµÕ≥µƒ÷˜“™Ãÿµ„£¨∏þ–ß÷ß≥÷∂˛Ω¯÷∆∑≠“ΰ£ 1.1 ºƒ¥Ê∆˜ LoongArch Œ™RISC÷∏¡ÓºØ£¨”–32∏ˆÕ®”√ºƒ¥Ê∆˜°¢32∏ˆ∏°µ„/œÚ¡øºƒ¥Ê∆˜°£∆‰÷–r0µƒ÷µŒ™0£¨PCµƒ÷µ «µ±«∞÷∏¡Óµÿ÷∑£¨÷ªƒÐ±ª◊™“∆÷∏¡Ó£¨“Ï≥£œð»Î∫Õ“Ï≥£∑µªÿº‰Ω”–Þ∏ƒ°£ºƒ¥Ê∆˜øÌ∂»‘⁄LA32œ¬ «32±»Ãÿ£¨‘⁄LA64œ¬ «64±»Ãÿ°£ |

|

|

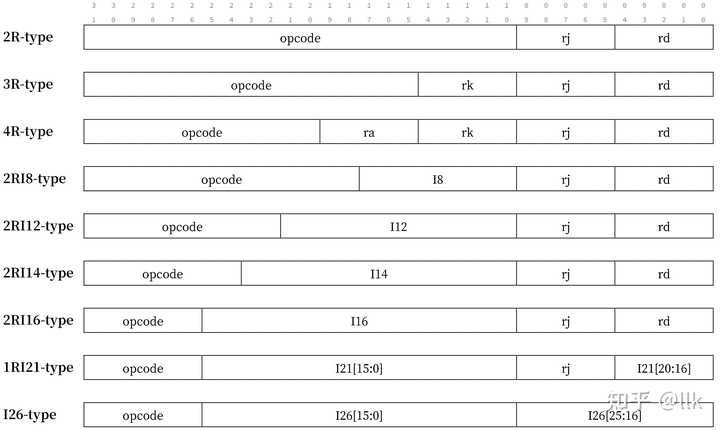

1.2 º∆À„ƒ£ Ω ¡˙–æºÐππ∑÷Œ™LA32∫ÕLA64¡Ω÷÷º∆À„ƒ£ Ω£¨LA64ø…“‘ºÊ»ðLA32µƒ”¶”√≤„»Ìº˛£¨æþÔ…CSR.MISC.VA32L1/VA32L2/VA32L3øÿ÷∆£¨µ±’‚–©÷µŒ™1 ±£¨‘À––‘⁄PLV1/PLV2/PLV3º∂œ¬µƒ»Ìº˛æÕ“‘32Œªµÿ÷∑ƒ£ Ω‘À––°£¥À ±”≤º˛Ω´∑√¥Ê–ȃ‚µÿ÷∑µÕ32Œª¡„¿©’π÷¡64Œª÷Æ∫Ûµƒ÷µ◊˜Œ™∑√¥Êµƒµÿ÷∑°£ 1.3 ÷∏¡Ó∏Ò Ω MIPS÷ª”–3÷÷÷∏¡Ó∏Ò Ω£¨LoongArch÷ÿ–¬…˺∆¡À÷∏¡Ó∏Ò Ω £¨ π”√32Œª∂®≥§÷∏¡Ó£¨ø…”√µƒ∏Ò Ω∂ý¥Ô9÷÷ £¨∆‰∞¸∫¨3÷÷ŒÞ¡¢º¥ ˝∏Ò Ω∫Õ6÷÷”–¡¢º¥ ˝∏Ò Ω°£÷ÿ–¬…˺∆µƒ÷∏¡Ó∏Ò Ωø…“‘∞¸∫¨∏¸∂ýµƒ÷∏¡Ó≤€£¨”–¿˚”⁄“‘∫Ûµƒ≥§‘∂∑¢’π°£÷∏¡Ó±ý¬Î∏Ò Ω»Áœ¬±ÌÀ˘ æ£∫ |

|

|

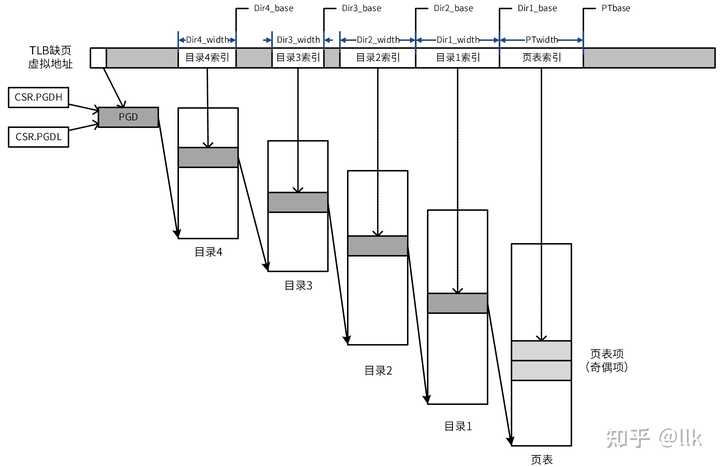

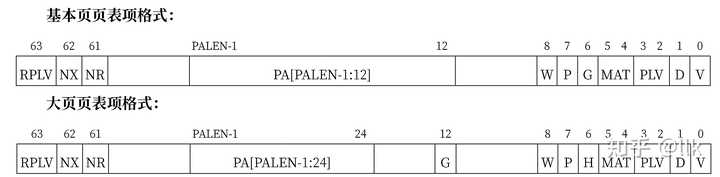

1.4 Ãÿ»®ƒ£–Õ ¡˙–æºÐππ∑÷Œ™4∏ˆÃÿ»®µ»º∂£¨∑÷± «PLV0~PLV3£¨”…CSR.CRMD.PLV »∑∂®°£∆‰÷–£¨PLV0æþ”–◊Ó∏þÃÿ»®µ»º∂£¨ø…“‘ π”√Ãÿ»®÷∏¡Ó≤¢∑√Œ À˘”–Ãÿ»®◊ ‘¥°£PLV1~PLV3£¨∂º≤ªƒÐ÷¥––Ãÿ»®÷∏¡Ó∫Õ∑√Œ Ãÿ»®◊ ‘¥£¨‘⁄MMU≤…”√”≥…‰µÿ÷∑∑≠“΃£ Ωœ¬æþ”–≤ªÕ¨µƒ∑√Œ »®œÞ°£ 1.5 ¥Ê¥¢ƒ£–Õ ¡˙–æºÐππµƒ¥Ê¥¢“ª÷¬–‘ƒ£–Õ≤…”√»ı“ª÷¬–‘(Weakly Consistency)ƒ£–Õ£¨≥Öڱÿ–Î π”√Õ¨≤Ω÷∏¡Ó∂‘–¥π≤œÌµ•‘™µƒ∑√Œ ±£ª§∆¿¥£¨“‘±£÷§∂‘”⁄–¥π≤œÌµ•‘™µƒ∑√Œ «ª•≥‚µƒ°£∂‘∑√¥ÊµƒÀ≥–ÚœÞ÷∆»Áœ¬£∫ Õ¨≤Ω÷∏¡Óµƒ÷¥––¬˙◊„À≥–Ú“ª÷¬–‘Ãıº˛£¨º¥Õ¨≤Ω≤Ÿ◊˜‘⁄À˘”–¥¶¿Ì∆˜∫À÷–∂º—œ∏Ò∞¥’’≥ÖÚÀ≥–Ú÷¥––£¨‘⁄µ±«∞Õ¨≤Ω÷∏¡ÓÕÍ≥…÷Æ«∞≤ªƒÐø™ º÷¥––œ¬“ª∏ˆÕ¨≤Ω≤Ÿ◊˜ ‘⁄»Œ“ª∑√¥Ê÷∏¡Ó±ª÷¥––÷Æ«∞£¨∏√÷∏¡Ó÷Æ«∞µƒÕ¨≤Ω÷∏¡Ó“—æ≠ÕÍ≥… ‘⁄»Œ“ªÕ¨≤Ω÷∏¡Ó±ª÷¥––÷Æ«∞£¨∏√÷∏¡Ó÷Æ«∞µƒ∑√¥Ê÷∏¡Ó∂º“—ÕÍ≥… ¡˙–æºÐππœ¬÷ß≥÷»˝÷÷¥Ê¥¢∑√Œ ¿ý–Õ£¨”…“≥±Ì÷–MAT(Memory Access Type) æˆ∂®£¨∑÷± «: “ª÷¬ø…ª∫¥Ê(Coherent Cached) ∑√Œ ∂‘œÛø…“‘ «÷˜¥Ê“≤ø…“‘ «ª∫¥Ê «ø–Ú∑«ª∫¥Ê(Strongly-ordered UnCached) —œ∏Ò∞¥’’≥ÖÚÀ≥–Ú÷¥–– »ı–Ú∑«ª∫¥Ê(Weakly-ordered UnCached) ∂¡‘ –ÌÕ∂ª˙÷¥––£¨–¥ø…“‘∫œ≤¢1.6 ƒ⁄¥Êπп̺∞–ȃ‚ªØ ¡˙–æºÐππMMUµÿ÷∑∑≠“Δ…CSR.CRMDøÿ÷∆£¨ µ±CSR.CRMD.DA=1 && CSR.CRMD.PG=0 ±£¨–ȃ‚µÿ÷∑æÕ «ŒÔ¿Ìµÿ÷∑ µ±CSR.CRMD.DA=0 && CSR.CRMD.PG=1 ±£¨–ȃ‚µÿ÷∑–Ë“™æ≠π˝∑≠“Σ¨ø…“‘∑÷Œ™÷±Ω””≥…‰∫Õ“≥±Ì”≥…‰1.6.1 ÷±Ω””≥…‰µÿ÷∑∑≠“΃£ Ω »Ìº˛Õ®π˝…Ë÷√CSR.DMW0~CSR.DMW3ºƒ¥Ê∆˜¿¥∑÷±…Ë÷√Àƒ∏ˆ÷±Ω””≥…‰≈‰÷√¥∞ø⁄£¨«∞¡Ω∏ˆÕ¨ ±”√”⁄»°÷∏∫եʥ¢º”‘ÿ÷∏¡Ó£¨∫Û¡Ω∏ˆ÷ª◊˜”√”⁄¥Ê¥¢º”‘ÿ÷∏¡Ó°£ ‘⁄LA64ºÐππœ¬£¨µ±–ȃ‚µÿ÷∑◊Ó∏þ4Œª[63:60]”Î≈‰÷√¥∞ø⁄ºƒ¥Ê∆˜÷–µƒVSEG”Úœýµ»«“Ãÿ»®µ»º∂∆•≈‰ ±£¨ŒÔ¿Ìµÿ÷∑µ»”⁄–ȃ‚µÿ÷∑µƒ[PALEN-1:0]°£ ‘⁄LA32ºÐππœ¬£¨√ø“ª∏ˆ÷±Ω””≥…‰≈‰÷√¥∞ø⁄ºƒ¥Ê∆˜ø…“‘≈‰÷√“ª∏ˆ$2^{29}$◊÷Ω⁄πÃ∂®¥Û–°µƒ–ȃ‚µÿ÷∑ø’º‰£¨µ±–ȃ‚µÿ÷∑µƒ◊Ó∏þ3Œª[31:29]”Î≈‰÷√¥∞ø⁄ºƒ¥Ê∆˜÷–µƒ[31:29]œýµ»«“Ãÿ»®µ»º∂∆•≈‰ ±£¨ŒÔ¿Ìµÿ÷∑µ»”⁄–ȃ‚µÿ÷∑[28:0]∆¥Ω”…œ”≥…‰≈‰÷√ºƒ¥Ê∆˜≈‰÷√µƒŒÔ¿Ìµÿ÷∑∏þŒª°£ 1.6.2 “≥±Ì”≥…‰ ¡˙–æºÐππœ¬TLBµƒ÷ÿÃÓ“‘º∞TLB”΃⁄¥Ê“≥±Ìµƒ“ª÷¬–‘Œ¨ª§»´≤ø–Ë“™»Ìº˛ÕÍ≥…£¨∂ýº∂“≥±ÌΩ·ππ»Áœ¬À˘ æ£∫ |

|

|

µ±±È¿˙“≥±Ì ±£¨PGD”…–ȃ‚µÿ÷∑$PALEN-1$æˆ∂®£¨ µ±VA[PALEN-1]=0 ±£¨PGD¿¥◊‘CSR.PGDL µ±VA[PALEN-1]=1 ±£¨PGD¿¥◊‘CSR.PGDH “≥±ÌœÓ∏Ò Ω»Áœ¬±ÌÀ˘ æ£∫ |

|

|

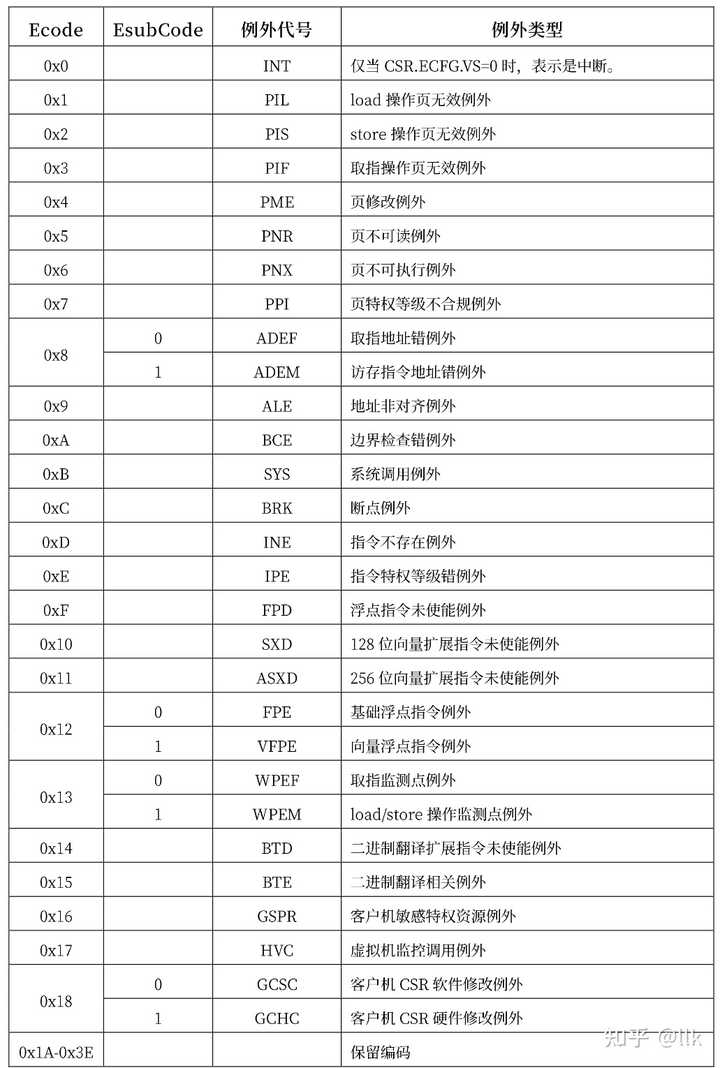

1.7 “Ï≥£∫Õ÷–∂œ “Ï≥£∫Õ÷–∂œª·¥Ú∂œµ±«∞’˝‘⁄÷¥––µƒ”¶”√≥Öڣ¨≤¢«–ªªµΩ“Ï≥£÷–∂œ¥¶¿Ì≥ÖڻÎø⁄ø™ º÷¥––£¨“Ï≥£∫Õ÷–∂œ Ù”⁄ºÐππ÷–Ãÿ»®◊ ‘¥¥¶¿Ì≤ø∑÷£¨œ¬√Ê÷˜“™ΩÈ…Ð≥£”√“ª–©“Ï≥££∫ œµÕ≥µ˜”√“Ï≥£ ÷¥––SYSCALL ÷∏¡Ó¥•∑¢ ∂œµ„“Ï≥£ ÷¥––BREAK÷∏¡Ó¥•∑¢ ÷∏¡Ó≤ª¥Ê‘⁄“Ï≥£ À˘÷¥––µƒ÷∏¡Ó±ý¬ÎŒ¥∂®“ ±¥•∑¢ Ãÿ»®÷∏¡Ó¥Ì“Ï≥£ ‘⁄∑«Ãÿ»®ƒ£ Ωœ¬÷¥––Ãÿ»®÷∏¡Ó ±¥•∑¢ µÿ÷∑¥Ì“Ï≥£ µ±»°÷∏ªÚ∑√¥Ê÷∏¡Óµƒµÿ÷∑≥ˆœ÷∑÷∑¢«Èøˆ ±£¨∑÷±ª·¥•∑¢»°÷∏÷∏¡Óµÿ÷∑¥Ì“Ï≥£ªÚ∑√¥Ê÷∏¡Óµÿ÷∑¥Ì“Ï≥£ ∏°µ„¥Ì“Ï≥£ µ±∏°µ„÷∏¡Óµƒ ˝æð≥ˆœ÷“Ï≥£«Èøˆ–Ë“™Ãÿ ‚¥¶¿Ì ±¥•∑¢1.7.1 “Ï≥£∫Õ÷–∂œ¥¶¿Ì TLB÷ÿÃÓ“Ï≥£µƒ»Îø⁄µÿ÷∑ «CSR.TLBRENTRY, ª˙∆˜¥ÌŒÛ“Ï≥£µƒ»Îø⁄ «CSR.MERRENTRY£¨∆‰À˚“Ï≥£≥∆Œ™∆’Õ®“Ï≥££¨»Îø⁄µÿ÷∑µ»”⁄$»Îø⁄“≥∫≈ | “≥ƒ⁄∆´“∆$ £¨À˘”–∆’Õ®“Ï≥£µƒ»Îø⁄“≥∫≈∂º «CSR.EENTRY £ª∂¯“≥ƒ⁄∆´“∆”…÷–∂œ∆´“∆ƒ£ Ω∫Õ“Ï≥£∫≈(ecode)π≤Õ¨æˆ∂®£¨µ»”⁄$2^{CSR.ECFG.VS+2} * (ecode+64)$ °£÷–∂œ±ªµ±≥…∆’Õ®“Ï≥£¥¶¿Ì£¨“Ú¥À π”√∆’Õ®“Ï≥£µƒ»Îø⁄º∆À„∑Ω Ω£¨«¯± «£¨÷–∂œ∂‘”¶µƒ“Ï≥£∫≈ «∂‘”¶÷–∂œ∫≈º”…œ64°£“Ï≥£ecode»Áœ¬±ÌÀ˘ æ£∫ |

|

|

¥•∑¢“Ï≥£µƒ÷∏¡Óµƒµÿ÷∑ª·±ªº«¬ºµΩERA¿Ô£¨◊˜Œ™“Ï≥£∑µªÿµÿ÷∑£ª∂‘”⁄µÿ÷∑¥ÌŒÛœýπÿµƒ“Ï≥££¨≥ˆ¥Ìµƒµÿ÷∑ª·±ªº«¬ºµΩBADV°£¥•∑¢“Ï≥£µƒ÷∏¡Óª·±ªº«¬ºµΩBADI¿Ô°£ 2. Godson-1 ¡˙–æµ⁄“ªøÓ¥¶¿Ì∆˜¡˙–æ1∫≈…˺∆”⁄2001ƒÍ£¨2002ƒÍ∑¢≤º£¨ «“ªøÓ32Œªµ•∑¢…‰¬“–Ú÷¥––CPU£¨÷˜∆µ266MHz°£—ß ı¬€Œƒ…œ¥˙∫≈ «Godson-1£¨ «÷–π˙ø∆—ß‘∫÷™ ∂¥¥–¬π§≥Ã∑ΩœÚ–‘œÓƒø”Îπ˙º“°∞∞À¡˘»˝°±∏þºº ı—–æø∑¢’πº∆ªÆœÓƒøµƒ—–æø≥…π˚°£À¸≤…”√ 0.18 Œ¢√◊ CMOS 𧓒÷∆‘Ï£¨æþ”– 8 KB L1D°¢8 KB L1I ∫Õ“ª∏ˆ 64 Œª∏°µ„µ•‘™£¨ƒÐπª¥ÔµΩ 200 À´æ´∂» MFLOPS°£œ¬Õº’π æ¡ÀGodson-1µƒŒÔ¿ÌπʪÆ∞ÊÕº£∫ |

|

|

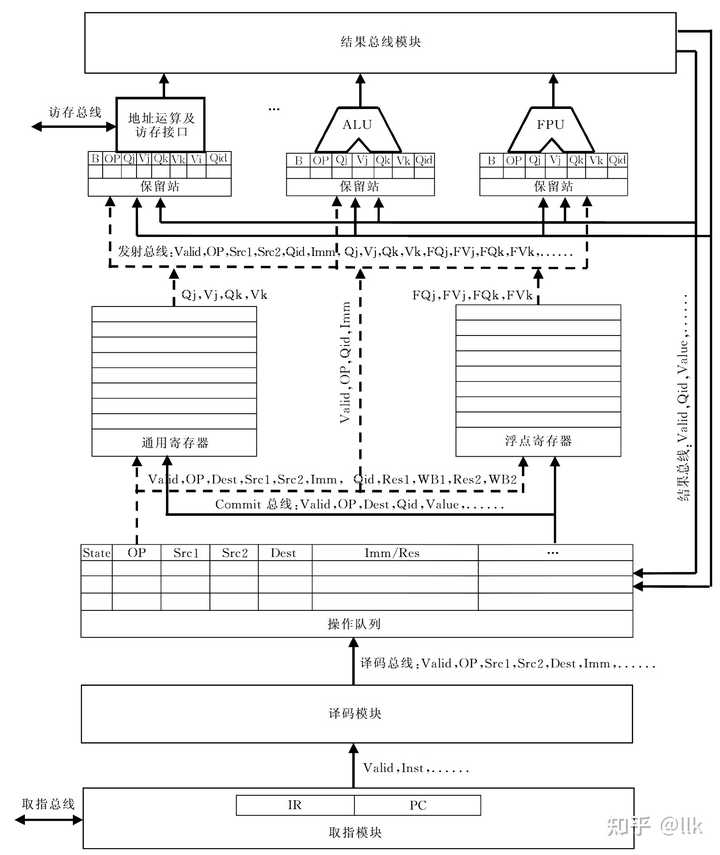

¡˙–æ1∫≈ µœ÷ª˘”⁄≤Ÿ◊˜∂”¡–∏¥”√µƒºƒ¥Ê∆˜÷ÿ√¸√˚ºº ı£¨≤…”√TomasuloÀ„∑®Ω¯––∂Ø赘∂»£¨∑÷÷ß‘§≤‚ π”√æ≤葧≤‚£¨º¥√ø¥Œ∂º‘§≤‚∑÷÷ß÷¥––°£÷˜“™”…»°÷µµ•‘™£¨“άε•‘™£¨≤Ÿ◊˜∂”¡–£¨∂®µ„∫Õ∏°µ„ºƒ¥Ê∆˜Œƒº˛∫Õ∂®µ„∏°µ„÷¥––µ•‘™◊È≥…°£œ¬Õº’π æ¡ÀGodson-1µƒŒ¢ºÐππ£∫ |

|

|

÷∏¡Ó“άε•‘™∞¥≥ÖÚÀ≥–ÚΩ´“άÎ∫Û÷∏¡Ó∑÷∑¢µΩ≤Ÿ◊˜∂”¡–£¨≤Ÿ◊˜∂”¡–∏˘æð÷∏¡Ó¿ý–Õ∑¢…‰µΩ∂‘”¶µƒ±£¡Ù’棨≤¢∞¥–ÚΩ· ¯“—æ≠ÕÍ≥…µƒ÷∏¡Ó°£±£¡Ù’æ÷–µƒ÷∏¡Óæ≠π˝÷¥––µ•‘™÷Æ∫Û£¨Ω·π˚–¥ªÿµΩ≤Ÿ◊˜∂”¡–∫ÕΩ·π˚◊Ðœþ°£»Áπ˚÷∏¡Ó∑¢…‰ ±‘¥≤Ÿ◊˜ ˝ªπ√ª”–◊º±∏∫√£¨≤¢≤ªª·◊Ë÷π÷∏¡Óµƒ∑¢…‰£¨∂¯ «Õ®π˝≤Ÿ◊˜∂”¡–∫≈Ω®¡¢÷∏¡Óº‰µƒ ˝æð“¿¿µπÿœµ≤¢∑¢…‰µΩ±£¡Ù’棪±£¡Ù’æ◊‘∂Ø’ÏÃ˝◊ÐœþΩ·π˚≤¢Ω” ÐÀ˘–Ë“™µƒ÷µ£¨æþÃÂπ˝≥ûÁœ¬£∫ ÷∏¡ÓΩ¯»Î≤Ÿ◊˜∂”¡– ±Ω´∏√÷∏¡Óµƒµƒ‘¥ºƒ¥Ê∆˜∫≈”Î≤Ÿ◊˜∂”¡–÷–µƒ√ø“ª∏ˆ÷∏¡Óµƒƒø±Íºƒ¥Ê∆˜∫≈Ω¯––±»Ωœ£¨µ√µΩ≤Ÿ◊˜∂”¡–÷–◊ÓΩ¸µƒ–¥∏√ºƒ¥Ê∆˜µƒ÷∏¡ÓµƒŒª÷√Qid ÷∏¡Ó∑¢…‰ ±ºÏ≤ÈQidµƒ÷µ£¨»Áπ˚“—æ≠–¥ªÿµΩ≤Ÿ◊˜∂”¡–‘Ú÷±Ω”∂¡≥ˆ£¨∑Ò‘ÚΩ´QidÀÕµΩ±£¡Ù’æ≤¢º«¬º÷µŒ¥◊º±∏∫√ µ±±£¡Ù’æ÷–À˘”–≤Ÿ◊˜ ˝∂º◊º±∏∫√∫Ûø™ º‘ÀÀ„≤¢∞—Ω·π˚ÀÕµΩΩ·π˚◊Ðœþ£¨∂‘”¶≤Ÿ◊˜∂”¡–∫Õ±£¡Ù’æ ÷∏¡Ó¡˜ÀÆœþ∑÷≥…»°÷µ£¨“άΣ¨÷ÿ√¸√˚£¨∑¢…‰£¨÷¥––£¨–¥ªÿ£¨ÕÍ≥…µ»Ω◊∂Œ£¨∆‰÷–÷¥––Ω◊∂Œø…ƒÐ–Ë“™∂ý≈ƒ£¨æþûÁœ¬£∫ »°÷µ ∏˘æ𵱫∞≥Öں∆ ˝∆˜PCΩ´÷∏¡Ó¥”ª∫¥Ê∂¡µΩ÷∏¡Óºƒ¥Ê∆˜IR£¨ŒÞ∑÷÷ß÷∏¡Óº∞“Ï≥£«Èøˆœ¬£¨œ¬“ªÃı÷∏¡ÓµƒPCŒ™µ±«∞÷∏¡ÓµƒPC+4 “άΠ∏˘æðIR÷–µƒ÷∏¡ÓΩ¯––“άÎ≤¢–¥»Î≤Ÿ◊˜∂”¡–£¨»Áπ˚≤Ÿ◊˜∂”¡–“—¬˙£¨¡˜ÀÆœþ‘ðÕ£ ÷ÿ√¸√˚ ∏√÷∏¡Óµƒµƒ‘¥ºƒ¥Ê∆˜∫≈”Î≤Ÿ◊˜∂”¡–÷–µƒ√ø“ª∏ˆ÷∏¡Óµƒƒø±Íºƒ¥Ê∆˜∫≈Ω¯––±»Ωœ£¨µ√µΩ≤Ÿ◊˜∂”¡–÷–◊ÓΩ¸µƒ–¥∏√ºƒ¥Ê∆˜µƒ÷∏¡ÓµƒŒª÷√Qid ∑¢…‰ ¥”≤Ÿ◊˜∂”¡–÷–—°≥ˆ“ª∏ˆ÷∏¡Ó≤¢∑¢…‰µΩœý”¶µƒ±£¡Ù’棨»Áπ˚÷∏¡Ó‘¥≤Ÿ◊˜ ˝≤ªø…”√£¨‘Ú–Ë“™±£¡Ù’溫¬º÷µŒ¥◊º±∏∫√ ÷¥–– ÷¥––µ•‘™¥”±£¡Ù’æ÷–»°≥ˆÀ˘”–‘¥≤Ÿ◊˜ ˝∂º◊º±∏∫√µƒ÷∏¡ÓΩ¯––‘ÀÀ„£¨≤¢Ω´Ω·π˚º∞÷∏¡Ó‘⁄≤Ÿ◊˜∂”¡–Œª÷√±ý∫≈ÀÕµΩΩ·π˚ºƒ¥Ê∆˜ –¥ªÿ ∞—Ω·π˚ºƒ¥Ê∆˜µƒ÷µ“‘º∞œý”¶÷∏¡Ó‘⁄≤Ÿ◊˜∂”¡–Œª÷√±ý∫≈ÀÕµΩΩ·π˚◊Ðœþ£¨±£¡Ù’æ∫Õ≤Ÿ◊˜∂”¡–’ÏÃ˝Ω·π˚◊Ðœþµƒ–≈œ¢£¨≤¢∏¸–¬œý”¶◊¥Ã¨ Ω· ¯ »Áπ˚≤Ÿ◊˜∂”¡–÷–µƒµ⁄“ª∏ˆ÷∏¡Ó“—æ≠ÕÍ≥…£¨‘ÚΩ· ¯∏√÷∏¡Ó≤¢Ω´≤Ÿ◊˜∂”¡–¿ÔµƒΩ·π˚–¥ªÿµΩƒø±Íºƒ¥Ê∆˜°£»Áπ˚≤Ÿ◊˜∂”¡–÷–µƒµ⁄“ª∏ˆ÷∏¡Ó‘⁄÷¥––π˝≥Ã÷–∑¢…˙“Ï≥££¨‘ÚΩ¯––“Ï≥£¥¶¿Ì3. Godson-2 ∫Õ Godson-3 ¡˙–æ2F”⁄2007ƒÍ7‘¬31»’¡˜∆¨≥…𶣨90ƒ…√◊𧓒£¨4∑¢…‰¬“–Ú÷¥––£¨√ʪ˝ $43mm^2$ £¨¡˙–æ2F «¡˙–æµ⁄“ªøÓ≥…𶵃…Ô√¥¶¿Ì∆˜°£œ¬Õº’π æ¡ÀGodson-2EµƒŒÔ¿ÌπʪÆÕº£∫ |

|

|

œ¬Õº’π æ¡ÀGodson-2FµƒŒÔ¿ÌπʪÆÕº£∫ |

|

|

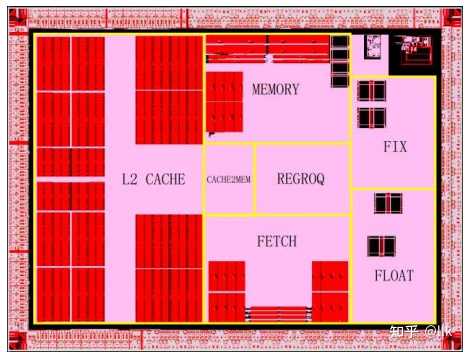

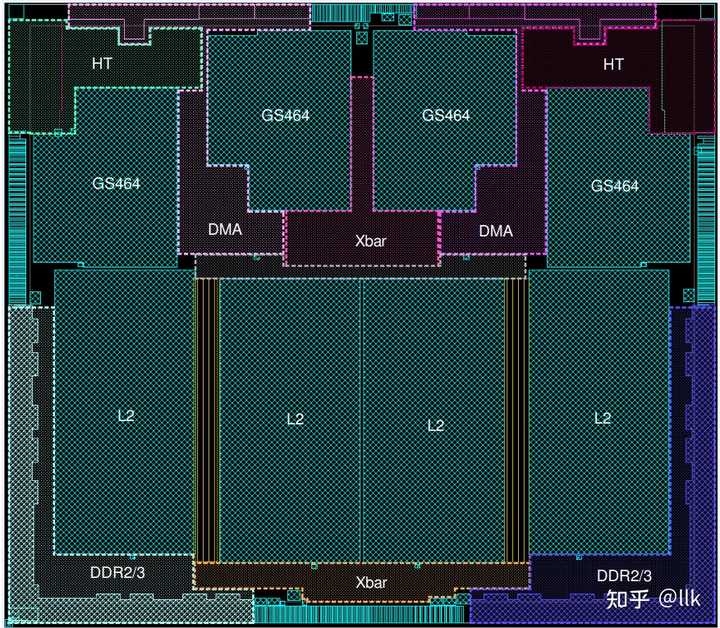

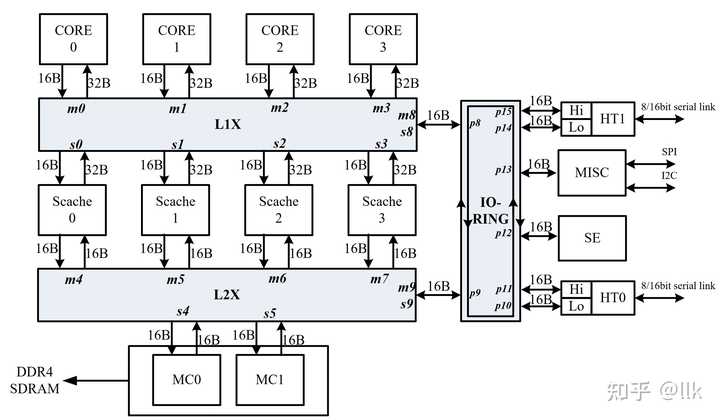

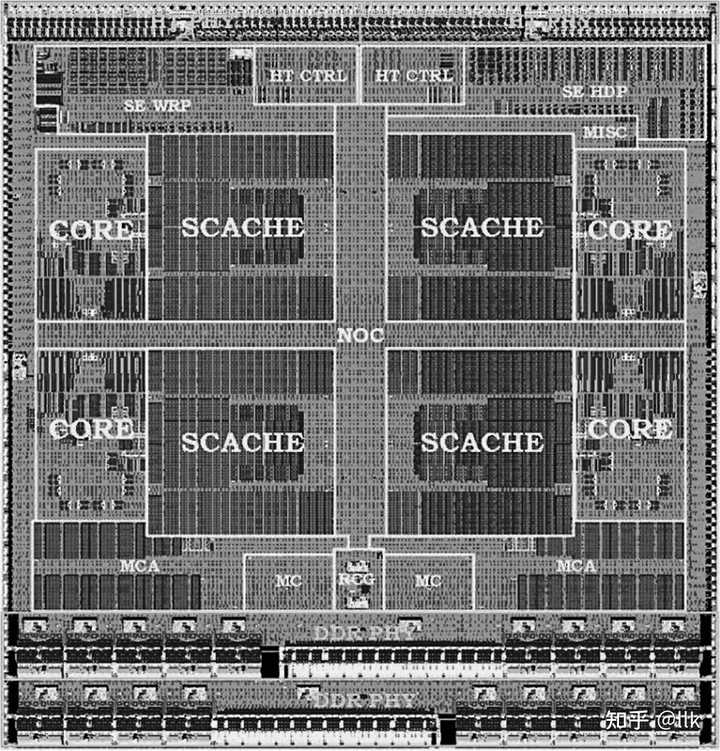

¡˙–æ2G «‘⁄°∞¡˙–æ∞≤»´ ”√º∆À„ª˙CPU—–÷∆”Δ¶”√°±∫À∏þª˘÷ÿ¥Û◊®œÓøŒÃ‚÷ß≥÷œ¬—–∑¢µƒ£¨2008ƒÍø™ ºÕ∂»Î…˺∆£¨2010ƒÍ—–÷∆≥…π¶°£¡˙–æ2G≤…”√65ƒ…√◊𧓒£¨÷˜∆µ1.0GHz£¨æßÃÂπÐ ˝ƒø1“⁄£¨÷∏¡ÓºØºÊ»ðMIPS64£¨«“‘ˆº”¡ÀX86∂˛Ω¯÷∆∑≠“κ”ÀŸ÷∏¡Ó£¨“‘º∞¡˙–æ√Ωÿ©’π÷∏¡Ó£¨”–64KBµƒ÷∏¡Ó∫Õ64KB ˝æðµƒL1ª∫¥Ê£¨“‘º∞1MBµƒL2ª∫¥Ê£¨π¶∫ƒ3W°£‘⁄∏√¥¶¿Ì∆˜…œ£¨ π”√¡ÀX86∂˛Ω¯÷∆∑≠“κº ı£¨Ã·≥ˆ¡À‘⁄MIPS∆Ωî…œ µœ÷X86∂Øè∂˛Ω¯÷∆∑≠“εƒ∑Ω∑®°£¡˙–æ2Gœýµ±”⁄¡˙–æ3A1000µƒµ•∫À∞ʱ氣¡˙–æ3A1000”⁄2008ƒÍµ◊Ωª∏∂¡˜∆¨,≤…”√“‚∑®∞εºÃµƒ65nm𧓒¡˜∆¨£¨÷˜∆µ800MHz-1GHz°£¡˙–æ3A1000Ω¯––¡Àµ⁄“ª¥Œ∏ƒ∞Ê≤¢”⁄2010ƒÍ5‘¬÷–—Æ¡˜∆¨£¨10‘¬µ◊µ⁄“ª¥Œ∏ƒ∞Ê¡˜∆¨≥…π¶°£3A1000µƒµ⁄∂˛¥Œ∏ƒ∞Ê”⁄2012ƒÍ2‘¬œ¬—Æ¡˜∆¨£¨2012ƒÍ8‘¬÷–—Æ¡˜∆¨≥…π¶°£ ¡˙–æ3A1000ºØ≥…¡À4∏ˆÀƒ∑¢…‰¬“–Ú÷¥––µƒGS464∫À£¨9º∂¡˜ÀÆœþ£¨”–64KB“ªº∂ ˝æðª∫¥Ê∫Õ64KB“ªº∂÷∏¡Óª∫¥Ê£¨4MBπ≤œÌ∂˛º∂ª∫¥Ê£¨◊Ó∏þ÷˜∆µ1GHz£¨π¶∫ƒ15w£®÷ß≥÷∂ØÃ¨Ωµ∆µ£©£¨–æ∆¨√ʪ˝ $174mm^2$ £¨æßÃÂπÐ ˝ƒø4.25“⁄°£√ø∏ˆCPU∫À∞¸∫¨¡Ω∏ˆ∏°µ„≥Àº”≤øº˛£¨À´æ´∂»∏°µ„–‘ƒÐ∑Â÷µŒ™16GFlops°£‘⁄¡˙–æ3A1000¥¶¿Ì∆˜÷–£¨ µœ÷¡Àx86∂˛Ω¯÷∆∑≠“κ”ÀŸ÷∏¡Ó°£3A1000ºØ≥…¡ÀPCIøÿ÷∆∆˜°¢LPC°¢SPI°¢UART°¢GPIO∫Õ2∏ˆHT1.0£ªºØ≥…72ŒªDDR2/3øÿ÷∆∆˜°£œ¬Õº’π æ¡ÀGodson-3A1000µƒŒÔ¿ÌπʪÆ∞ÊÕº£∫ |

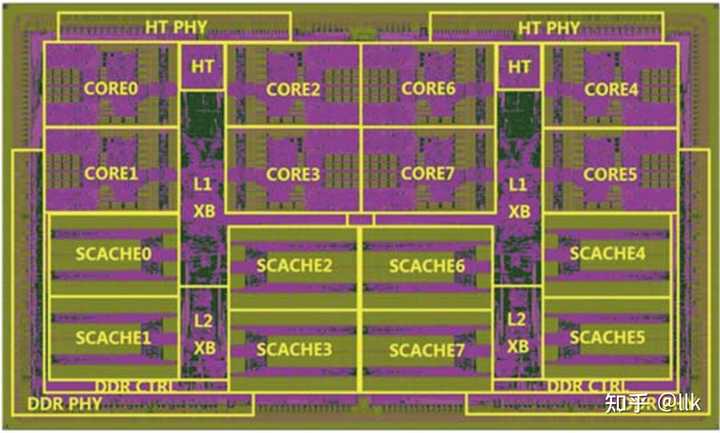

|

|

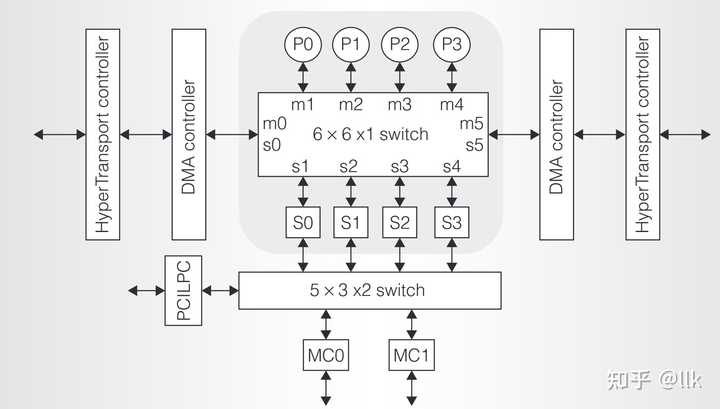

¡˙–æ3A1000µ⁄“ªº∂ª•¡™≤…”√6x6µƒΩª≤Êø™πÿ£¨”√”⁄4∏ˆ¥¶¿Ì∆˜∫À£¨4∏ˆπ≤œÌª∫¥Êƒ£øÈ∫Õ¡Ω∏ˆIO∂Àø⁄µƒ¡¨Ω”°£µ⁄∂˛º∂ª•¡™≤…”√5x3µƒΩª≤Êø™πÿ£¨¡¨Ω”4∏ˆπ≤œÌµƒª∫¥Êƒ£øÈ£¨¡Ω∏ˆƒ⁄¥Êøÿ÷∆∆˜∫Õ“ª∏ˆIO∂Àø⁄°£œ¬Õº’π æ¡À¡˙–æ3A1000’˚úÐππ£∫ |

|

|

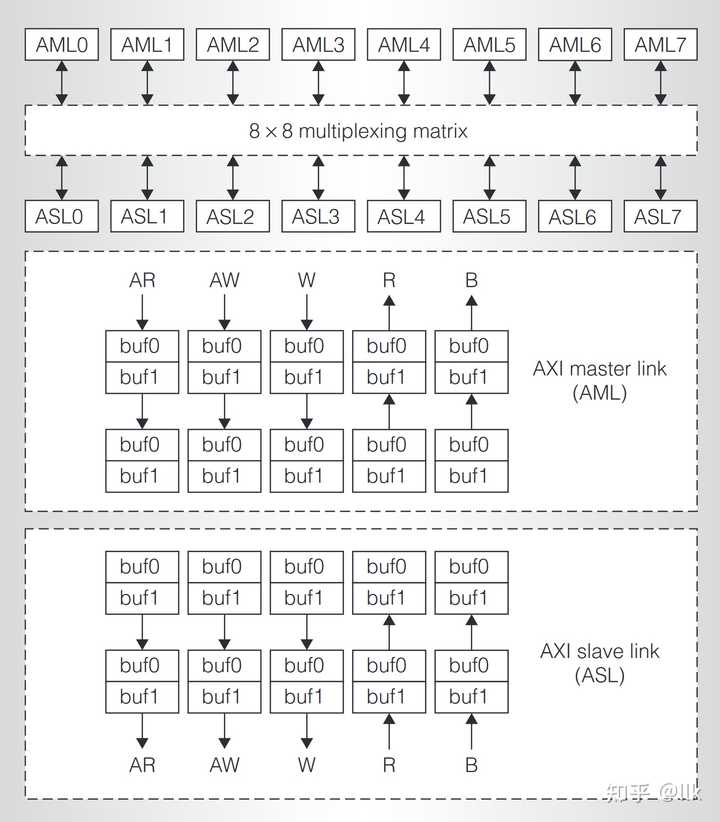

œ¬Õº’π æ¡À“ª∏ˆ8x8Ωª≤ʪ•¡™µƒºÐππ£∫ |

|

|

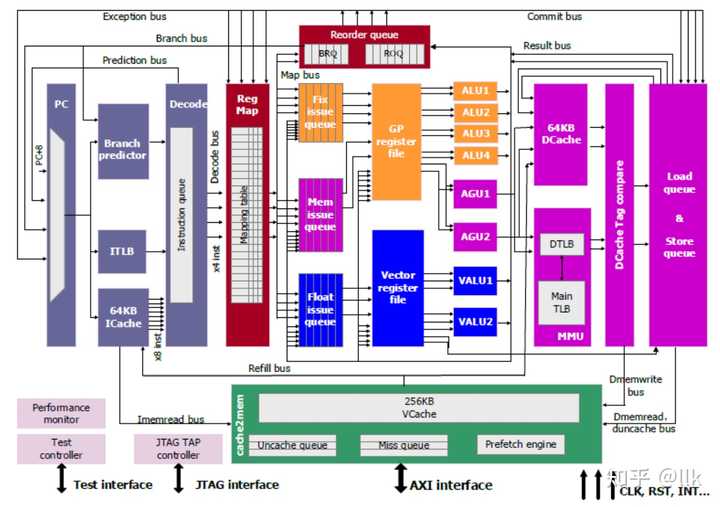

8∏ˆAXI master link(AML) ∫Õ 8∏ˆAXI slave link(ASL) Õ®π˝“ª∏ˆΩª≤Êø™πÿΩ¯––ª•¡™£¨AML π”√∂¡–¥«Î«Ûµƒµÿ÷∑–≈œ¢Ω¯––¬∑”…£¨∂¡–¥∏˜”–8∏ˆµÿ÷∑«¯º‰£¨∂‘”¶ASL°£ASLÕ®π˝œý”¶«Î«ÛµƒAML ∂Àø⁄∫≈Ω´∂¡–¥œÏ”¶¬∑”…µΩ∂‘”¶µƒAML°£AML∫ÕASL∏˜”–¡Ωº∂¡˜ÀÆ£¨À˘“‘Ωª≤ʪ•¡™“ªπ≤”–4∏ˆ÷Ð∆⁄—”≥Ÿ°£ 3.1 GS464Œ¢ºÐππ œ¬Õº’π æ¡ÀGS464µƒŒ¢ºÐππ£∫ |

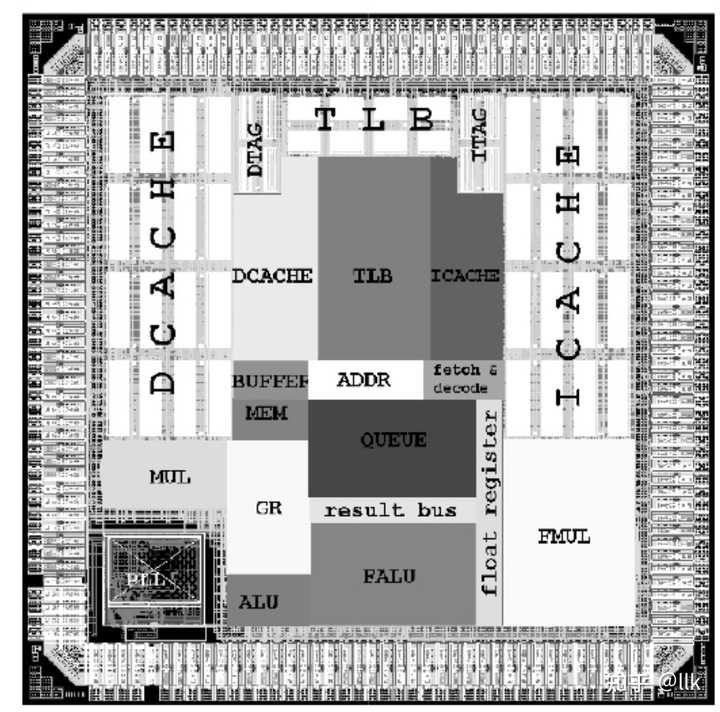

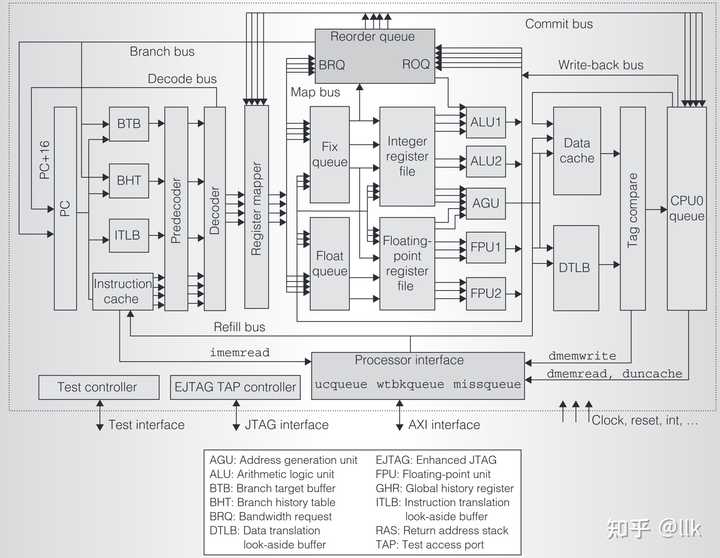

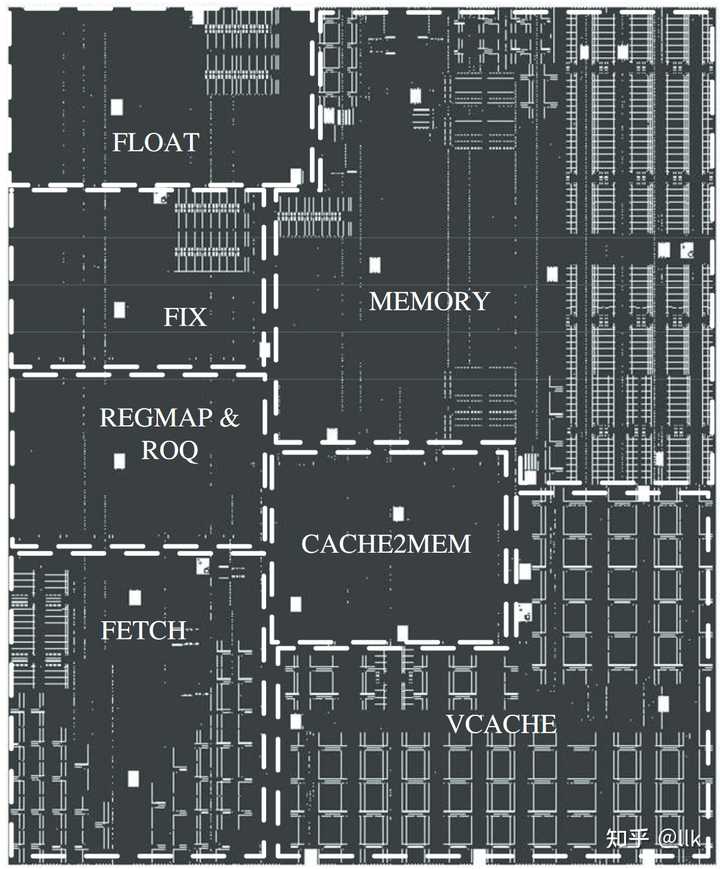

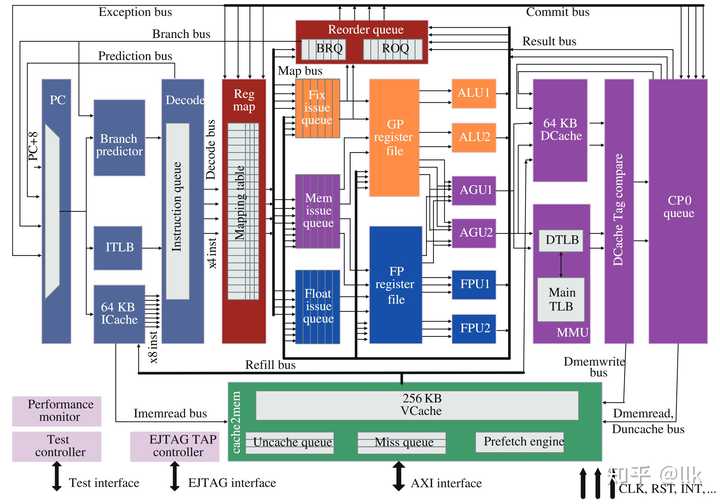

|

|

÷∏¡Ó¡˜ÀÆœþ∑÷≥…»°÷µ£¨“άΣ¨÷ÿ√¸√˚£¨∑¢…‰£¨÷¥––£¨–¥ªÿ£¨ÕÍ≥…µ»Ω◊∂Œ£¨∆‰÷–÷¥––Ω◊∂Œø…ƒÐ–Ë“™∂ý≈ƒ£¨æþûÁœ¬£∫ »°÷µ ∏˘æ𵱫∞≥Öں∆ ˝∆˜PCΩ´÷∏¡Ó¥”ª∫¥Ê∂¡µΩ÷∏¡Óºƒ¥Ê∆˜IR£¨ŒÞ∑÷÷ß÷∏¡Óº∞“Ï≥£«Èøˆœ¬£¨œ¬“ªÃı÷∏¡ÓµƒPCŒ™µ±«∞÷∏¡ÓµƒPC+16 ‘§“άΠ∂‘÷∏¡Ó…®√Ë£¨ ∂±≥ˆ∑÷÷ß÷∏¡Ó≤¢∂‘∆‰∑÷÷ß∑ΩœÚΩ¯––‘§≤‚ “άΠ∏˘æðIR÷–µƒ4Ãı÷∏¡ÓΩ¯––“άÎ≤¢ÀÕµΩºƒ¥Ê∆˜÷ÿ√¸√˚ƒ£øÈ ÷ÿ√¸√˚ Ω´ºÐππºƒ¥Ê∆˜”≥…‰µΩŒÔ¿Ìºƒ¥Ê∆˜…œ ∑÷∑¢ ºƒ¥Ê∆˜÷ÿ√¸√˚÷Æ∫Ûµƒ÷∏¡Ó±ª∑÷∑¢µΩ∂®µ„ªÚ∏°µ„±£¡Ù’æ“‘±„÷¥––£¨Õ¨ ±ÀÕµΩ÷ÿ∂®–Ú∂”¡–“‘±„À≥–ÚÕÍ≥…£ª∑÷÷ß∫եʥ¢º”‘ÿ÷∏¡Ó±ª∑÷∑¢µΩ∂‘”¶µƒ∑÷÷ß∂”¡–∫եʥ¢º”‘ÿ∂”¡–°£±£¡Ù’æ∫Õ∑¢…‰∂”¡–√øœÓø…±£¥Ê∑÷∑¢4Ãı÷∏¡Ó ∑¢…‰ ¥”±£¡Ù’æ÷–—°≥ˆ≤Ÿ◊˜ ˝∂º◊º±∏∫√«“◊Ó¿œµƒ“ª∏ˆ÷∏¡Ó≤¢∑¢ÀÕµΩœý”¶µƒ÷¥––µ•‘™£¨»Áπ˚÷∏¡Ó‘¥≤Ÿ◊˜ ˝≤ªø…”√£¨‘Ú’ÏÃ˝Ω·π˚∫Õ«∞¿°◊Ðœþ ÷¥–– ÷¥––µ•‘™¥”±£¡Ù’æ÷–»°≥ˆÀ˘”–‘¥≤Ÿ◊˜ ˝∂º◊º±∏∫√µƒ÷∏¡ÓΩ¯––‘ÀÀ„£¨≤¢Ω´Ω·π˚∑¢ÀÕµΩΩ·π˚∫Õ«∞¿°◊Ðœþ Ω· ¯ √ø÷Ð∆⁄ø…ÕÍ≥…4Ãı÷∏¡Ó£¨ÕÍ≥…µƒ÷∏¡ÓµƒΩ·π˚±ª∑¢ÀÕµΩºƒ¥Ê∆˜”≥…‰ƒ£øÈ“‘±„∏¸–¬ºÐππºƒ¥Ê∆˜Õ¨ ± Õ∑≈◊ ‘¥3.1.1 »°÷∏∫Õ∑÷÷ß‘§≤‚ GS464∞¸∫¨ 1 ∏ˆ4 ¬∑◊Èœý¡™ 64 KB µƒ÷∏¡Óª∫¥Ê, ∆‰ª∫¥Ê––¥Û–°Œ™ 32 ◊÷Ω⁄, ÷∏¡Óª∫¥Êµƒ±Í«©∫Õ ˝æð≤ø∑÷Õ¨ ±∑√Œ ≤¢‘⁄œ¬“ª ±÷”÷Ð∆⁄Ω¯––√¸÷–µƒ≈–∂œ”Η°‘Ò°£∆‰÷– ˝æð≤ø∑÷ªÆ∑÷Œ™ 8 ∏ˆbank£¨√ø¥Œ»°÷∏¡Ó ±÷ª”√∂¡»°À˘–Ë“™µƒbank, ΩµµÕ¡Àª∫¥Ê∑√Œ ±µƒ∂Øèπ¶∫ƒ°£÷∏¡Óª∫¥Ê π”√–ȵÿ÷∑À˜“˝∫Õ µµÿ÷∑±Í ∂µƒÀ˜“˝∑Ω∞∏°£»°÷∏≤øº˛µƒ–È µµÿ÷∑◊™ªªÕ®π˝ 16 œÓ»´œý¡™Ω·ππµƒ÷∏¡Ó TLB ÕÍ≥…, ÷∏¡Ó TLB ÷–µƒƒ⁄»ð «“≥±Ìµƒ◊”ºØ°£∆‰÷–, √øœÓ¥Ê∑≈ 1 ∏ˆ“≥±ÌœÓ, √ø∏ˆ“≥±ÌœÓæ˘ø…÷ß≥÷ 4 KB-1 GB ÷ƺ‰≤ªÕ¨¥Û–°µƒ“≥°£µ±÷∏¡Óª∫¥Ê√¸÷– ±, »°÷∏≤øº˛√ø∏ˆ ±÷”÷Ð∆⁄◊Ó∂ýø…“‘¥”÷∏¡Óª∫¥Ê÷–»°≥ˆ 4 Ãı÷∏¡Ó, ≤¢ÀÕÕ˘œ¬ “ª∏ˆ¡˜Àƺ∂Ω¯––∑÷÷ß‘§≤‚. ∂¯µ±÷∏¡Óª∫¥ÊŒ¥√¸÷– ±, »°÷∏≤øº˛Ω´…˙≥…«Î«Û≤¢∑√Œ ª∫¥Ê ß–ß∂”¡–, ∑√¥Ê ß–ß∂”¡–∏∫‘Ω¯––ª∫¥Ê»± ߥ¶¿Ì, ≤¢Ω´Ω·π˚∑µªÿ∏¯÷∏¡Óª∫¥Ê°£¥”ª∫¥Ê ß–ß∂”∑µªÿµƒΩ·π˚Ω´’˚ÃÂÃÓªÿ÷∏¡Óª∫¥Ê£¨ ÷∏¡Óª∫¥Ê◊Ó∂ýø…»ð»Ã 3 ∏ˆª∫¥Ê––≤ª√¸÷–, º¥”– 3 ∏ˆŒ¥ÕÍ≥… (outstanding) µƒª∫¥Ê––≤ª√¸÷– ±, “¿æ…ø…“‘¥”’˝»∑µƒµÿ÷∑»°÷∏¡Ó°£µ±»°÷∏«Î«Û«°∫√¬‰‘⁄¥”ª∫¥Ê ß–ß∂”¡–∑µªÿµƒª∫¥Ê«Î«Û ˝æð…œ ±, ø…“‘÷±Ω”»°≥ˆœý”¶÷∏¡ÓΩ¯»Îœ¬“ª∏ˆ¡˜Àƺ∂°£¥À Õ‚, ÷∏¡Óª∫¥Êµƒ‘§»°”…ª∫¥Ê ß–ß∂”¡–÷–µƒ”≤º˛‘§»°“˝«ÊÕ≥“ªÕÍ≥…, ≤ª‘⁄»°÷∏≤øº˛÷–µ•∂¿Ω¯––°£÷∏¡Óª∫¥Êµƒ ˝æð≤ø∑÷÷–ªπ∞¸∫¨‘§“άΖ≈œ¢, √øÃı÷∏¡Óµƒ‘§“άΖ≈œ¢Œ™ 8±»Ãÿ¥Û–°, ÷˜“™”√”⁄÷∏¡Ó«–∑÷°¢∑÷÷ß¿ý–Õ≈–∂®∫Õ≤ø∑÷÷∏¡Ó¿˝Õ‚µƒ≈–∂®°£‘§“άΖ≈œ¢Õ®π˝‘⁄ª∫¥Ê ß–ß∂”¡–÷ÿÃÓ÷∏¡Óª∫¥Ê ±º∆À„µ√≥ˆ, ≤¢¥Ê¥¢‘⁄÷∏¡Óª∫¥Ê÷–°£ ‘⁄‘§“άÎΩ◊∂Œ£¨ª·…®√ËIR¿Ô4Ãı÷∏¡Ó÷–µƒ∑÷÷ß÷∏¡Ó≤¢‘§≤‚∑÷÷ß∑ΩœÚ∫Õ∑÷÷߃ø±Í£¨branch-like ∫Õ jump ÷∏¡Ó◊Ð «‘§≤‚÷¥––£¨∂‘”⁄Ãıº˛∑÷÷ß÷∏¡Ó£¨‘Ú π”√∑÷÷ß¿˙ ∑±Ì(BHT)¿¥‘§≤‚∑÷÷ß∑ΩœÚ£¨ π”√∑÷÷߃ø±Íª∫≥Â(BTB)∫Õ∑µªÿµÿ÷∑∂—’ª(RAS)‘§≤‚∑÷÷߃ø±Íµÿ÷∑°£BHT”…9±»Ãÿ»´æ÷¿˙ ∑ºƒ¥Ê∆˜(global history register) GHR ∫Õ4Kƒ£ Ω¿˙ ∑±Ì(pattern history table) PHT◊È≥…£¨PHT¿Ô√øœÓ”–2±»Ãÿµƒ±•∫Õº∆ ˝∆˜£¨∏þŒª”√”⁄∑÷÷ß∑ΩœÚ‘§≤‚°£BTB”–16œÓ£¨√ø“ªœÓ”…÷∏¡Óµÿ÷∑∫Õï◊™÷∏¡Óƒø±Íµÿ÷∑“‘º∞2±»Ãÿ±•∫Õº∆ ˝∆˜◊È≥…£¨º∆ ˝∆˜÷µŒ™0ªÚ1µƒœÓ ◊œ»±ªÃʪª°£RAS”–4œÓ£¨µ±”ˆµΩbranch and link ÷∏¡Ó ±£¨Ω´µ±«∞÷∏¡Óµÿ÷∑º”8Õ∆Ω¯RAS£¨∂¯”ˆµΩjump register 31 ÷∏¡Ó ±¥”RAS÷–µØ≥ˆ÷∏¡Óµÿ÷∑°£ ‘⁄“άÎΩ◊∂Œ£¨4Ãı÷∏¡Ó±ª“άÎ≤¢ÀÕµΩºƒ¥Ê∆˜÷ÿ√¸√˚ƒ£øÈ°£ 3.1.2 ºƒ¥Ê∆˜÷ÿ√¸√˚ GS464 π”√∫œ≤¢µƒºÐππ∫Õ÷ÿ√¸√˚ºƒ¥Ê∆˜∂—£¨∂®µ„∫Õ∏°µ„∑÷± «64œÓ£¨œý”¶ π”√64œÓµƒPRMT(physical register mapping tables)¿¥Œ¨ª§ºÐππ∫ՌԿ̺ƒ¥Ê∆˜÷ƺ‰”≥…‰πÿœµ°£PRMT√øœÓ∞¸∫¨: ◊¥Ã¨ √ø∏ˆŒÔ¿Ìºƒ¥Ê∆˜¥¶‘⁄œ¬¡–◊¥Ã¨÷Æ“ª£∫MAP_EMPTY£¨MAP_MAPPED, MAP_WTBK, MAP_COMMIT √˚◊÷ ŒÔ¿Ìºƒ¥Ê∆˜∂‘”¶µƒºÐππºƒ¥Ê∆˜±Í ∂ ”––ߌª »Áπ˚∂ý∏ˆŒÔ¿Ìºƒ¥Ê∆˜”≥…‰µΩ“ª∏ˆºÐππºƒ¥Ê∆˜£¨‘Ú±Í ∂◊Ó–¬µƒ ºƒ¥Ê∆˜÷ÿ√¸√˚ ±£¨–Ë“™≤È’“PRMT¿¥’“µΩ¡Ω∏ˆ‘¥ºƒ¥Ê∆˜src1,src2£¨ƒø±Íºƒ¥Ê∆˜dest ∂‘”¶µƒ◊Ó–¬”≥…‰µƒŒÔ¿Ìºƒ¥Ê∆˜psrc1, psrc2∫Õodest°£¡ÌÕ‚£¨“ª∏ˆ¥¶”⁄MAP_EMPTYµƒŒÔ¿Ìºƒ¥Ê∆˜pdest±ª”≥…‰µΩdest£¨«“◊¥Ã¨–Þ∏ƒŒ™MAP_MAPPED£¨”––ߌª÷√1£¨odest”––ߌª÷√0°£÷Æ∫Û”≥…‰µƒŒÔ¿Ìºƒ¥Ê∆˜±ªÀÕµΩ±£¡Ù’棨odest±£¥Ê‘⁄÷ÿ∂®–Ú∂”¡–“‘±„÷∏¡ÓΩ· ¯ ± Õ∑≈ŒÔ¿Ìºƒ¥Ê∆˜°£µ±÷∏¡Ó÷¥––ÕÍ≥… ±£¨∂‘”¶µƒPRMTœÓ◊¥Ã¨∏¸–¬Œ™MAP_WTBK, ÷∏ æ∫Û–¯“¿¿µ÷∏¡Óµƒ≤Ÿ◊˜ ˝◊º±∏∫√¡À°£µ±÷∏¡ÓÕÍ≥…∫Û£¨pdestµƒ◊¥Ã¨∏¸–¬Œ™MAP_COMMIT£¨odest∏¸–¬Œ™MAP_EMPTY°£ 3.1.2 ÷∏¡Ó∑¢…‰ GS464”–¡Ω∏ˆ±£¡Ù’棨∑÷± «∂®µ„∫եʥ¢º”‘ÿ±£¡Ù’æ∫Õ∏°µ„±£¡Ù’æ°£√ø∏ˆ±£¡Ù’æ”–16œÓ£¨√ø÷Ð∆⁄ø…Ω” ’4Ãı÷∏¡Ó°£√øœÓ∞¸∫¨“ª∏ˆƒÍ¡‰”Ú£¨µ±÷∏¡ÓΩ¯»Î±£¡Ù’æ ±…Ë÷√≥…◊Ó–°÷µ£¨µ±Õ¨“ª∏ˆπ¶ƒÐµ•‘™µƒ–¬÷∏¡ÓΩ¯»Î ±£¨æ…÷∏¡Óµƒ÷µº”“ª°£¥”±£¡Ù’æ÷–—°≥ˆ≤Ÿ◊˜ ˝∂º◊º±∏∫√«“◊Ó¿œµƒ“ª∏ˆ÷∏¡Ó≤¢∑¢ÀÕµΩœý”¶µƒ÷¥––µ•‘™£¨»Áπ˚÷∏¡Ó‘¥≤Ÿ◊˜ ˝≤ªø…”√£¨‘Ú’ÏÃ˝Ω·π˚∫Õ«∞¿°◊Ðœþ ∂‘”⁄∑÷÷ß÷∏¡Ó£¨≥˝¡À∑¢ÀÕµΩ±£¡Ù’æ∫Õ÷ÿ∂®–Ú∂”¡–÷ÆÕ‚£¨ªπª·Ω¯»Î∑÷÷ß∂”¡–£¨√ø÷Ð∆⁄ø…Ω” ’“ªÃı∑÷÷ß÷∏¡Ó£¨Õ¨ ±◊Ó∂ý±£¥Ê8Ãı∑÷÷ß÷∏¡Ó°£µ±∑÷÷ß÷∏¡Ó÷¥–– ±£¨Ω·π˚–¥ªÿµΩ∑÷÷ß∂”¡–£¨∞¸¿®JR∫ÕJALR÷∏¡Óµƒµÿ÷∑£¨Ãıº˛∑÷÷ßµƒ∑÷÷ß∑ΩœÚ£¨“‘º∞‘§≤‚ «∑Ò’˝»∑°£√ø“ª∏ˆ÷∏¡Ó∂ºª·∑÷≈‰“ª∏ˆbrqid£¨∂‘”⁄∑÷÷ß÷∏¡Ó£¨÷∏ æ‘⁄∑÷÷ß∂”¡–µƒŒª÷√£¨∂‘”⁄∆‰À˚÷∏¡Ó£¨±Í ∂¡À∏√÷∏¡Ó«∞“ª∏ˆ∑÷÷ß÷∏¡ÓµƒŒª÷√°£µ±∑÷÷ß‘§≤‚¥ÌŒÛ ±£¨∏√∑÷÷ß÷∏¡Ó÷Æ∫Ûµƒ÷∏¡Ó∂ºª·±ª»°œ˚°£ 3.1.3 ÷∏¡ÓÕÍ≥… ºƒ¥Ê∆˜÷ÿ√¸√˚÷Æ∫Û÷∏¡Ó∂º±ª±£¥Ê‘⁄÷ÿ∂®–Ú∂”¡–£¨÷±µΩ÷∏¡ÓÕÍ≥…°£µ±÷∏¡Ó÷¥––Ω· ¯«“–¥ªÿ∫Û£¨÷ÿ∂®–Ú∂”¡–∞¥’’≥ÖÚÀ≥–ÚÕÍ≥…£¨÷ÿ∂®–Ú∂”¡–“ªπ≤ø…“‘±£¥Ê32Ãı÷∏¡Ó£¨√ø÷Ð∆⁄ø…Ω” ’4Ãı÷∏¡Ó°£–¬Ω¯»Îµƒ÷∏¡Ó¥¶”⁄ROQ_MAPPED◊¥Ã¨£¨µ±÷∏¡ÓΩ·π˚–¥ªÿ ±∫Û£¨∂‘”⁄∑÷÷ß÷∏¡Ó£¨◊¥Ã¨∏¸–¬Œ™ROQ_BRWTBK£¨∆‰À˚÷∏¡Ó‘Ú∏¸–¬≥…ROQ_WTBK°£∂‘”⁄∑÷÷ß÷∏¡Ó£¨÷ª”–∑÷÷ßΩ·π˚»∑∂®«“∂‘”⁄‘§≤‚¥ÌŒÛµƒ∑÷÷ß÷∏¡Ó≥ÂÀ¢¡˜ÀÆœþ÷Æ∫Û≤≈ª·∏¸–¬≥…ROQ_WTBK°£µ±÷∏¡ÓµΩ¥Ô÷ÿ∂®–Ú∂”¡–∂”Õ∑«“¥¶”⁄ROQ_WTBK ±≤≈ø…“‘Ω· ¯°£√ø÷Ð∆⁄ø…ÕÍ≥…4Ãı÷∏¡Ó°£µ±÷∏¡ÓÕÍ≥… ±£¨pdest∫Õodest∑¢ÀÕµΩºƒ¥Ê∆˜÷ÿ√¸√˚ƒ£øÈ“‘±„∏¸–¬¥¶¿Ì∆˜ºÐππ◊¥Ã¨≤¢ Õ∑≈odestœÓ°£∂‘”⁄≤˙…˙“Ï≥£µƒ÷∏¡Ó£¨“≤ª·‘⁄÷∏¡ÓµΩ¥Ô∂”Õ∑ ±¥¶¿Ì°£ 3.1.4 ∑√¥Ê∂”¡– GS464”–64Kµƒ÷∏¡Óª∫¥Ê∫Õ ˝æðª∫¥Ê£¨∂º «4¬∑◊Èœý¡™£ª64œÓµƒTLB£¨Œ™»´œý¡™Ω·ππ°£∑√¥Ê∂”¡–“ªπ≤”–16œÓ£¨◊Ó∂ýø…“‘∏˙◊Ÿ16Ãı¥Ê¥¢º”‘ÿ÷∏¡Ó°£µ±º”‘ÿ÷∏¡ÓΩ¯»Î∂”¡– ±£¨ª·ºÏ≤ÈÀ˘”–∏¸¿œµƒ¥Ê¥¢÷∏¡Ó£ªµ±¥Ê¥¢÷∏¡ÓΩ¯»Î∂”¡– ±£¨ª·ºÏ≤ÈÀ˘”–∏¸ƒÍ«·µƒº”‘ÿ÷∏¡Ó°£ 4. Loongson 3B1000∫Õ3B1500 ¡˙–æ3B1000”…∫À∏þª˘œÓƒøøŒÃ‚°∞∏þ–‘ƒÐ∂ý∫ÀCPU—–∑¢”Δ¶”√°±÷ß≥÷£¨≤…”√“‚∑®∞εºÃÂ65ƒ…√◊𧓒…˺∆£¨÷˜∆µ1GHz£¨π¶∫ƒ25W£¨∆¨ƒ⁄ºØ≥…8∏ˆ64ŒªÀƒ∑¢…‰¬“–Ú÷¥––¡˙–æœÚ¡ø¥¶¿Ì∆˜∫ÀGS464V£¨4MBµƒ∂˛º∂ª∫¥Ê£¨√ø∏ˆ∫À∞¸∫¨¡Ω∏ˆ256ŒªœÚ¡ø≤øº˛£¨∑Â÷µ∏°µ„–‘ƒÐ¥ÔµΩ128GFLOPS°£¡˙–æ3B1000µƒ◊Ó¥ÛÃÿ…´ «¡˙–æœÚ¡ø¥¶¿Ì∆˜∫Àµƒ…˺∆£¨∏√¥¶¿Ì∆˜∫ÀΩ´GS464∫Àµƒµƒ∏°µ„≤øº˛∫Õ∏°µ„ºƒ¥Ê∆˜∂—ÃʪªŒ™2∏ˆ256ŒªµƒœÚ¡ø¥¶¿Ì≤øº˛∫Õ1∏ˆ128x256ŒªµƒœÚ¡øºƒ¥Ê∆˜∂—£¨ π¡˙–æ3B‘⁄1GHzœ¬µƒ∑Â÷µÀ´æ´∂»∏°µ„º∆À„ƒÐ¡¶¥ÔµΩ128GFlops°£‘⁄¡˙–æ3B1000¥¶¿Ì∆˜÷–£¨ µœ÷¡À300∂ýÃı◊®”√µƒœÚ¡ø¥¶¿Ì÷∏¡Ó°£¡˙–æ3B1000–æ∆¨√ʪ˝ $300mm^2$ , æßÃÂπÐ ˝ƒøΩ”Ω¸6“⁄°£ ¡˙–æ3B1500ºØ≥…¡À8∏ˆÀƒ∑¢…‰¬“–Ú÷¥––µƒ64ŒªGS464V¥¶¿Ì∆˜∫À£¨9º∂¡˜ÀÆœþ£¨√ø∏ˆ¥¶¿Ì∆˜∫À”–64KBµƒÀΩ”–“ªº∂÷∏¡Óª∫¥Ê∫Õ64KBµƒÀΩ”–“ªº∂ ˝æðª∫¥Ê£¨128KBÀΩ”–∂˛º∂ª∫¥Ê£¨”–8MB»˝º∂π≤œÌª∫¥Ê£¨≤…”√÷––æπ˙º 32ƒ…√◊𧓒…˙≤˙£¨–æ∆¨√ʪ˝ $180mm^2$ , æßÃÂπÐ ˝11“⁄£¨÷˜∆µ1.5GHz£¨µ•–æ∆¨À´æ´∂»∏°µ„º∆À„ƒÐ¡¶¥ÔµΩ192GFlops£¨π¶∫ƒ30w£®µ‰–Õ£©/60w£®œÚ¡ø£©°£ ”–2∏ˆHT2.0£¨PCI°¢LPC°¢SPI°¢UART°¢GPIO£¨72ŒªDDR2/3øÿ÷∆∆˜°£¡˙–æ3B1500”…2∏ˆ¥¶¿Ì∆˜Ω⁄µ„◊È≥…£¨√ø∏ˆ¥¶¿Ì∆˜Ω⁄µ„”–4∏ˆGS464V¥¶¿Ì∆˜∫À£¨¡Ω∏ˆ¥¶¿Ì∆˜Ω⁄µ„÷ƺ‰Õ®π˝Ωª≤Êø™πÿª•¡™°£œ¬Õº’π æ¡À¡˙–æ3B1500 ’˚úÐππÕº£∫ |

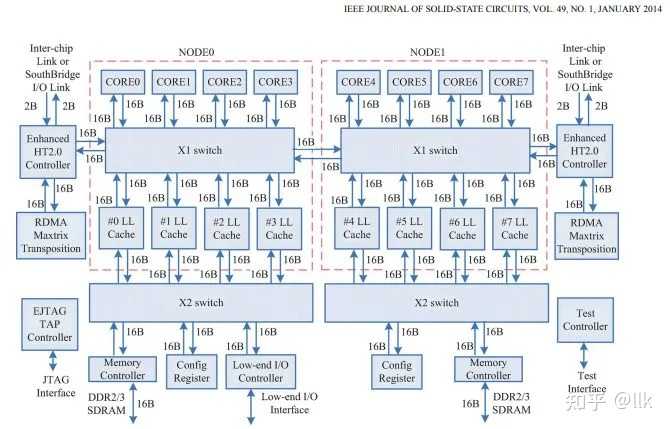

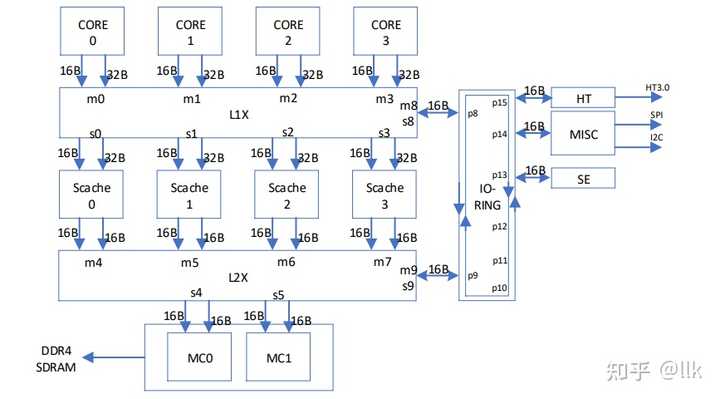

|

|

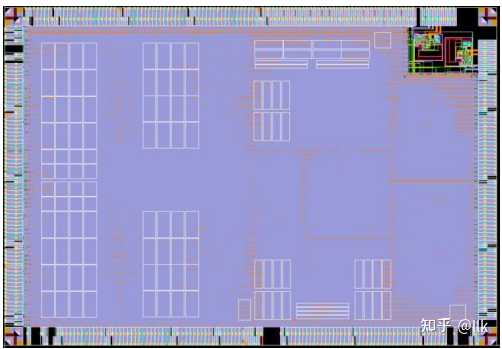

œ¬Õº’π æ¡À¡˙–æ3B1500ŒÔ¿Ì∞ÊÕº£∫ |

|

|

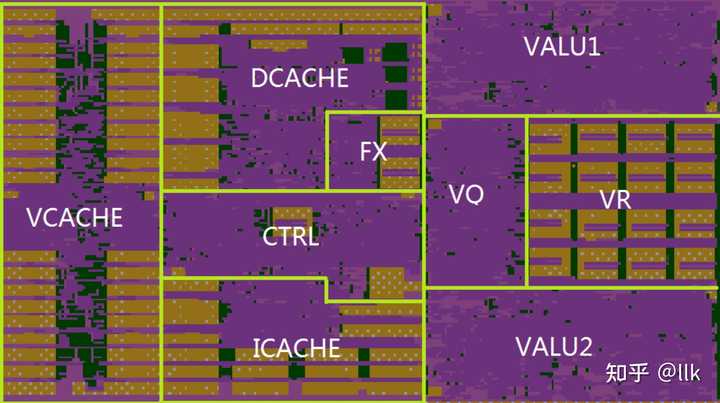

4.1 GS464VŒ¢ºÐππ GS464V‘⁄32nm𧓒œ¬√ʪ˝Œ™ $6.6mm^2$ £¨”–¡Ω∏ˆ256±»ÃÿµƒœÚ¡øÀ„ ıµ•‘™£¨√ø“ª∏ˆø…“‘÷¥––4∏ˆÀ´æ´∂»µƒ≥Àº”‘ÀÀ„£ª∂‘Õ‚ «“ª∏ˆ128±»ÃÿµƒAXIΩ”ø⁄°£œ¬Õº’π æ¡ÀGS464VµƒŒÔ¿ÌπʪÆÕº£∫ |

|

|

œ¬Õº’π æ¡ÀGS464VµƒŒ¢ºÐππ£¨∫ÕGS464µƒ«¯±æÕ «∏°µ„µ•‘™ªª≥…¡ÀœÚ¡øµ•‘™£¨∆‰À˚¡˜ÀÆœþ∂º «“ª—˘µƒ°£ |

|

|

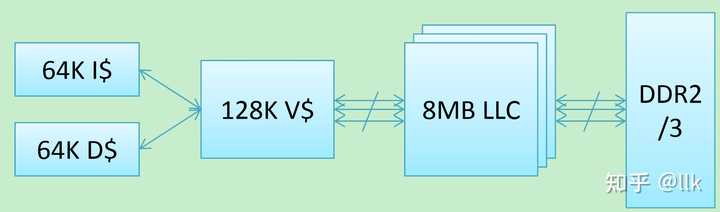

4.2 ¥Ê¥¢≤„¥Œ ¡˙–æ3B1500 √ø∏ˆGS464V¥¶¿Ì∆˜∫Àƒ⁄”–4¬∑◊Èœý¡™64KBµƒ÷∏¡Óª∫¥Ê£¨4¬∑◊Èœý¡™64KBµƒ ˝æðª∫¥Ê£¨“‘º∞4¬∑◊Èœý¡™◊˜Œ™victimª∫¥Êµƒ128KµƒL2ª∫¥Ê£ª8∏ˆGS464V¥¶¿Ì∆˜∫Àπ≤œÌ8MBµƒL3ª∫¥Ê°£ |

|

|

œ¬Õº’π æ¡À∏˜º∂¥Ê¥¢≤‚ ‘µƒ—”≥Ÿ£∫ |

|

|

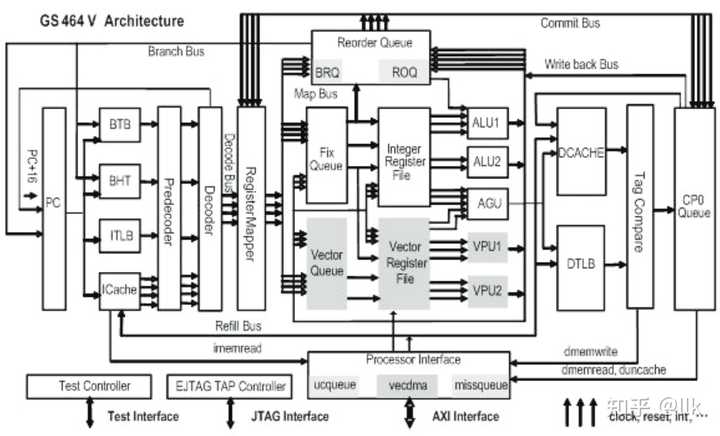

5. Loongson 3A2000 ¡˙–æ3A2000¥¶¿Ì∆˜ºØ≥…¡À4∏ˆÀƒ∑¢…‰¬“–Ú÷¥––64ŒªGS464E¥¶¿Ì∆˜∫À£¨“≤ « ◊øÓ≤…”√GS464EŒ¢Ω·π𵃥¶¿Ì∆˜°£ ≤…”√÷––æπ˙º 40ƒ…√◊CMOS𧓒…˙≤˙£¨÷˜∆µ800°´1000MHz GS464E¥¶¿Ì∆˜∫À «GS464µƒ∏ƒΩ¯∞Ê£¨ºØ≥…¡À64KB“ªº∂÷∏¡Óª∫¥Ê£¨64KB“ªº∂ ˝æðª∫¥Ê£¨256KB∂˛º∂ª∫¥Ê∫Õ4MB»˝º∂ª∫¥Ê°£¡˜ÀÆœþ¥”GS464µƒ9º∂÷∏þµΩ¡À12º∂°£∑Â÷µ∏°µ„–‘ƒÐ16GFlops°£‘⁄Ω”ø⁄…œ£¨¡˙–æ3A200ºØ≥…¡À¡Ω∏ˆHT3.0Ω”ø⁄£¨PCIøÿ÷∆∆˜°¢LPC°¢SPI°¢UART°¢GPIO£¨72ŒªDDR2/3-1333°¡2øÿ÷∆∆˜°£ 5.1 GS464EŒ¢ºÐππ Õ®π˝µ˜—–IBM POWER7µ»¥¶¿Ì∆˜£¨GS464Eœý±»”⁄÷Æ«∞µƒ GS464 ºÐππ, ÷ÿµ„«øªØ¡À∑√¥Ê–‘ƒÐ∫Õ∑÷÷ß‘§≤‚◊º»∑¬ , µœ÷¡À MIPS DSP ÷∏ ¡ÓºØ∫Ֆȃ‚ª˙÷ß≥÷, ‘ˆ¥Û¡À¥¶¿Ì∆˜÷–∏˜œÓ∂”¡–µƒœÓ ˝, ≤¢‘ˆ¥Û¡Àª∫¥Ê»ð¡ø∫Õ TLB »ð¡ø°£∑√¥Ê◊”œµÕ≥”µ”– 3 º∂ª∫¥ÊΩ·ππ, √ø“ªº∂∂º≤…”√ LRU Ãʪª≤þ¬‘, ø…“‘÷ß≥÷∂ý∫Àª∫¥Ê“ª÷¬–‘–≠“È°£œ¬Õº’π æ¡ÀGS464EµƒŒÔ¿ÌπʪÆÕº£¨÷˜“™”…»°÷∏µ•‘™£¨ºƒ¥Ê∆˜÷ÿ√¸√˚µ•‘™£¨∂®µ„µ•‘™£¨∏°µ„µ•‘™£¨∑√¥Êµ•‘™£¨L2ª∫¥Êµ»◊È≥…°£ |

|

|

”ÎGS464œý±»£¨GS464E ¥¶¿Ì∆˜∫À÷˜“™∏¸–¬: »°÷∏µ•‘™ »°÷∏µ•‘™µƒπ¶ƒÐ «Õ®π˝∑÷÷ß‘§≤‚≥÷–¯ªÒµ√÷∏¡Ó¡˜, ≤¢Ω¯––÷∏¡Ó“άÎ. ‘⁄ GS464E ¥¶¿Ì∆˜∫À÷–, Õ®π˝÷ÿ–¬…˺∆, œ˚≥˝¡À∑÷÷ß÷∏¡Ó‘§≤‚ï◊™∫Ûµƒ»°÷∏ø’≈ð; Õ®π˝º”»Î—≠ª∑ª∫≥Â∆˜ (loop buffer), πµ√◊Ó∂ý 56 Ãı÷∏¡Ó◊È≥…µƒ—≠ª∑≥ÖÚ÷¥–– ±≤ª–Ë∑√Œ ÷∏¡Óª∫¥Ê ºƒ¥Ê∆˜÷ÿ√¸√˚ ºƒ¥Ê∆˜÷ÿ√¸√˚≤øº˛µƒπ¶ƒÐ «Ω¯––∏˜÷÷ºƒ¥Ê∆˜µƒ÷ÿ√¸√˚, ”√”⁄∂Ø衘ÀÆœþ÷–µƒ¬“–Ú∑¢…‰°£GS464E ¥¶¿Ì∆˜∫À÷–µƒºƒ¥Ê∆˜÷ÿ√¸√˚±Ì¿©’πµΩ 128 œÓ∂®µ„ŒÔ¿Ìºƒ¥Ê∆˜∫Õ 128 œÓ∏°µ„ŒÔ¿Ìºƒ¥Ê∆˜, ¥ÀÕ‚, DSP øÿ÷∆ºƒ¥Ê∆˜°¢HILO ºƒ¥Ê∆˜“‘º∞∏°µ„±»ΩœΩ·π˚ºƒ¥Ê∆˜∂ºµ•∂¿Ω¯––÷ÿ√¸√˚ ÷∏¡Ó÷ÿ∂®–Ú ÷∏¡Ó÷ÿ∂®–Úµ•‘™µƒπ¶ƒÐ «Ω´¬“–Ú∑¢…‰µƒ÷∏¡ÓΩ¯––÷ÿ∂®–Ú, ≤¢Ω¯––∑÷÷ß‘§≤‚¥Ì”Î÷∏¡Ó“Ï≥£µƒ¥¶¿Ì. ÷∏¡Ó÷ÿ∂®–Ú∂”¡– (reorder queue, ROQ) ¥” 64 œÓ‘ˆ¥ÛµΩ 128 œÓ; ∑÷÷ß÷∏¡Ó∂”¡–¥” 8 œÓ ¿©¥ÛµΩ 24 œÓ ∂®µ„µ•‘™ ∂®µ„µ•‘™”√”⁄Ω¯––∂®µ„º∆À„. ‘⁄ GS464E ¥¶¿Ì∆˜∫À÷–, Õ®π˝º§Ω¯µƒº∆À„Ω·π˚÷«∞∑¥¿° (forward) ¬þº≠…˺∆, ¥Ê‘⁄ºƒ¥Ê∆˜ ˝æðœýπÿµƒ 2 Ãı∂®µ„÷∏¡Ó÷ƺ‰µƒ—”≥Ÿ (load-to-use) ¥” 2 ∏ˆ ±÷”÷Ð∆⁄ºı…ŸµΩ¡À 1 ∏ˆ; ¥ÀÕ‚ªπº”»Î¡À ˝◊÷–≈∫≈¥¶¿Ì (digital signal processing, DSP) π¶ƒÐµ•‘™ ∏°µ„µ•‘™ ∏°µ„µ•‘™”√”⁄Ω¯––∏°µ„º∆À„. ∏°µ„±»ΩœΩ·π˚ºƒ¥Ê∆˜œ÷‘⁄ø…“‘µ•∂¿Ω¯––÷ÿ√¸√˚, “Ú¥À∏°µ„±»Ωœ“‘º∞ π”√∏°µ„±»ΩœΩ·π˚µƒ÷∏¡Óø…“‘¬“–Ú∑¢…‰∫Õ∂Ø衘ÀÆ ∑√¥Êµ•‘™ ∑√¥Ê≤øº˛”√”⁄¥¶¿Ì∑√¥Ê÷∏¡Ó. ∑√¥Ê÷∏¡Ó◊®”√∑¢…‰∂”¡–¥Û–°Œ™ 32 œÓ, ø…“‘Ω´∑√¥Ê÷∏¡Ó¬“–Ú∑¢…‰µΩ 2 ∏ˆ∑√¥Êπ¶ƒÐ≤øº˛, √ø∏ˆπ¶ƒÐ≤øº˛æ˘ø…÷¥––∂¡»° (load) ªÚ¥Ê¥¢ (store) ÷∏¡Ó; ∑√¥Ê÷ÿ∂®–Ú∂”¡–µƒœÓ ˝¥” 24 œÓ÷…˝÷¡ 64 œÓ. “ªº∂ ˝æðª∫¥Ê≤…”√¡À LRU Ãʪª≤þ¬‘, ≤¢Ω´ ª∫¥Ê––¥Û–°¿©’πŒ™ 64 ◊÷Ω⁄≥§. µÿ÷∑∑≠“ÎøÏÀŸ≤È’“±Ì (translation lookaside buffer, TLB) µƒœÓ ˝“≤”–¥Û∑˘¿©≥‰, ≤…”√¡À 64 œÓø…±‰¥Û–°“≥Õ‚º” 1024 œÓπÃ∂®¥Û–°“≥µƒÀ´÷ÿ TLB …˺∆ ª∫¥Ê ß–ß∂”¡– ª∫¥Ê ß–ß∂”¡–”…÷∏¡Óª∫¥Ê ߖ߫Ϋ۔Π˝æðª∫¥Ê ߖ߫ΫÛÀ˘π≤”√, ”√”⁄¥¶¿Ìª∫¥Ê ß–ß≤¢÷ÿÃÓª∫¥Ê––. ‘⁄ GS464E ¥¶¿Ì∆˜∫À÷–, ∆‰œÓ ˝¥” 8 œÓ÷…˝÷¡ 16 œÓ, ≤¢ µœ÷¡Àº§Ω¯µƒ÷∏¡Ó∫Õ ˝æ𑧻°“˝«Ê, ∏√‘§»°“˝«Êª·∏˘æðª∫¥Ê ß–ß∂”¡–÷–µƒ–≈œ¢◊‘∂Ø…˙≥…‘§»°«Î«Û, ≤¢Õ®π˝ª∫¥Ê ß–ß∂”¡–¿¥¥¶¿Ì’‚–©‘§»°«Î«Û. ∏√‘§»°ª˙÷∆≤ªª·µº÷¬“ªº∂ª∫¥ÊŒ€»æ Victim Cache Victim Cache «∆¨ƒ⁄µƒµ⁄∂˛º∂ª∫¥Ê, µ±“ªº∂ª∫¥Ê ß–ß ±±ª≤È—Ø. ‘⁄ GS464E ¥¶¿Ì∆˜∫À÷–, ∆‰◊лð¡ø¿©¥ÛŒ™ 256 KB, œý¡™Ω·ππ¥” 8 ¬∑◊Èœý¡™∏ƒŒ™ 16 ¬∑◊Èœý¡™, ≤¢≤…”√¡À LRU Ãʪª≤þ¬‘, ÷∏þ¡À Victim Cache µƒ√¸÷–¬ œ¬Õº’π æ¡ÀGS464EµƒŒ¢ºÐππ£∫ |

|

|

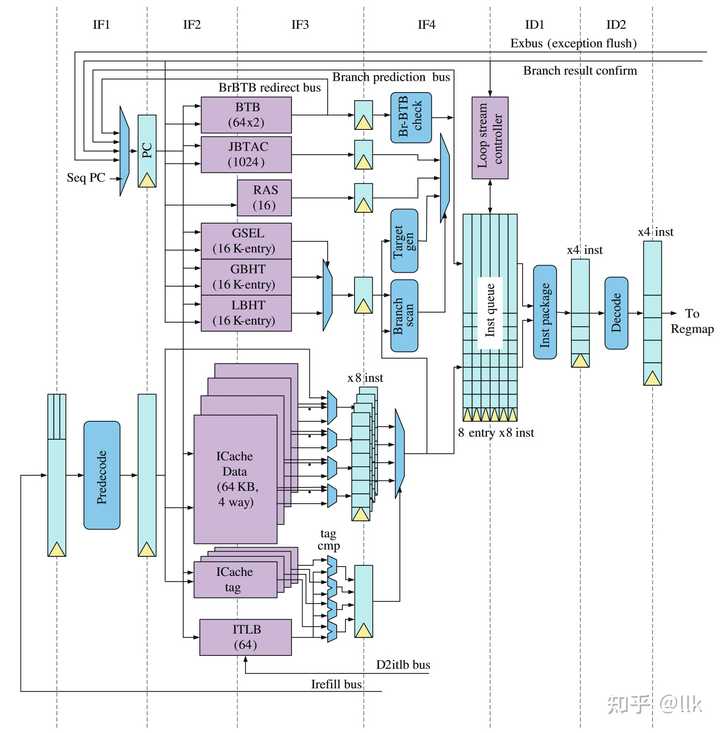

5.1.1 »°÷∏µ•‘™ GS464Eµƒ»°÷µµ•‘™÷˜“™∞¸¿®L1÷∏¡Óª∫¥Ê£¨÷∏¡ÓTLB£¨∑÷÷ß‘§≤‚∆˜£¨÷∏¡Ó∂”¡–∫Փάε•‘™°£œ¬Õº’π æ¡ÀGS464Eµƒ»°÷µµ•‘™µƒ¡˜ÀÆœþ£∫ |

|

|

√ø∏ˆ GS464E ¥¶¿Ì∆˜∫À∞¸∫¨ 1 ∏ˆ4 ¬∑◊Èœý¡™ 64 KB µƒ÷∏¡Óª∫¥Ê, ∆‰ª∫¥Ê––¥Û–°Œ™ 64 ◊÷Ω⁄, ÷∏¡Óª∫¥Êµƒ±Í«©∫Õ ˝æð≤ø∑÷Õ¨ ±∑√Œ ≤¢‘⁄œ¬“ª ±÷”÷Ð∆⁄Ω¯––√¸÷–µƒ≈–∂œ”Η°‘Ò°£∆‰÷– ˝æð≤ø∑÷ªÆ∑÷Œ™ 8 ∏ˆbank£¨√ø¥Œ»°÷∏¡Ó ±÷ª”√∂¡»°À˘–Ë“™µƒbank, ΩµµÕ¡Àª∫¥Ê∑√Œ ±µƒ∂Øèπ¶∫ƒ°£÷∏¡Óª∫¥Ê π”√–ȵÿ÷∑À˜“˝∫Õ µµÿ÷∑±Í ∂µƒÀ˜“˝∑Ω∞∏°£»°÷∏≤øº˛µƒ–È µµÿ÷∑◊™ªªÕ®π˝ 64 œÓ»´œý¡™Ω·ππµƒ÷∏¡Ó TLB ÕÍ≥…, ÷∏¡Ó TLB ÷–µƒƒ⁄»ð «“≥±Ìµƒ◊”ºØ°£∆‰÷–, √øœÓ¥Ê∑≈ 1 ∏ˆ“≥±ÌœÓ, √ø∏ˆ“≥±ÌœÓæ˘ø…÷ß≥÷ 4 KB-1 GB ÷ƺ‰≤ªÕ¨¥Û–°µƒ“≥°£µ±÷∏¡Óª∫¥Ê√¸÷– ±, »°÷∏≤øº˛√ø∏ˆ ±÷”÷Ð∆⁄◊Ó∂ýø…“‘¥”÷∏¡Óª∫¥Ê÷–»°≥ˆ 8 Ãı÷∏¡Ó, ≤¢ÀÕÕ˘œ¬ “ª∏ˆ¡˜Àƺ∂Ω¯––∑÷÷ß‘§≤‚. ∂¯µ±÷∏¡Óª∫¥ÊŒ¥√¸÷– ±, »°÷∏≤øº˛Ω´…˙≥…«Î«Û≤¢∑√Œ ª∫¥Ê ß–ß∂”¡–, ∑√¥Ê ß–ß∂”¡–∏∫‘Ω¯––ª∫¥Ê»± ߥ¶¿Ì, ≤¢Ω´Ω·π˚∑µªÿ∏¯÷∏¡Óª∫¥Ê°£¥”ª∫¥Ê ß–ß∂”∑µªÿµƒΩ·π˚Ω´’˚ÃÂÃÓªÿ÷∏¡Óª∫¥Ê£¨ ÷∏¡Óª∫¥Ê◊Ó∂ýø…»ð»Ã 3 ∏ˆª∫¥Ê––≤ª√¸÷–, º¥”– 3 ∏ˆŒ¥ÕÍ≥… (outstanding) µƒª∫¥Ê––≤ª√¸÷– ±, “¿æ…ø…“‘¥”’˝»∑µƒµÿ÷∑»°÷∏¡Ó°£µ±»°÷∏«Î«Û«°∫√¬‰‘⁄¥”ª∫¥Ê ß–ß∂”¡–∑µªÿµƒª∫¥Ê«Î«Û ˝æð…œ ±, ø…“‘÷±Ω”»°≥ˆœý”¶÷∏¡ÓΩ¯»Îœ¬“ª∏ˆ¡˜Àƺ∂°£¥À Õ‚, ÷∏¡Óª∫¥Êµƒ‘§»°”…ª∫¥Ê ß–ß∂”¡–÷–µƒ”≤º˛‘§»°“˝«ÊÕ≥“ªÕÍ≥…, ≤ª‘⁄»°÷∏≤øº˛÷–µ•∂¿Ω¯––°£÷∏¡Óª∫¥Êµƒ ˝æð≤ø∑÷÷–ªπ∞¸∫¨‘§“άΖ≈œ¢, √øÃı÷∏¡Óµƒ‘§“άΖ≈œ¢Œ™ 8±»Ãÿ¥Û–°, ÷˜“™”√”⁄÷∏¡Ó«–∑÷°¢∑÷÷ß¿ý–Õ≈–∂®∫Õ≤ø∑÷÷∏¡Ó¿˝Õ‚µƒ≈–∂®°£‘§“άΖ≈œ¢Õ®π˝‘⁄ª∫¥Ê ß–ß∂”¡–÷ÿÃÓ÷∏¡Óª∫¥Ê ±º∆À„µ√≥ˆ, ≤¢¥Ê¥¢‘⁄÷∏¡Óª∫¥Ê÷–°£ GS464E ¥¶¿Ì∆˜∫À≤…”√¡À∂ý÷÷≤ªÕ¨µƒª˙÷∆¿¥‘§≤‚∑÷÷ß÷∏¡ÓµƒÃ¯◊™∑ΩœÚ∫Õï◊™ƒø±Í, ≤¢Õ®π˝∑÷÷߃ø±Íª∫≥Â∆˜ (BrBTB) ¿¥¥¶¿Ì∑÷÷ß÷∏¡Ó÷Æ∫Û»°÷∏ø’≈𵃫Èøˆ°£∑÷÷ß‘§≤‚ª˙÷∆‘⁄√ø∏ˆ ±÷”÷Ð∆⁄◊Ó∂ýø…“‘¥¶¿Ì 4 Ãı∑÷÷ß÷∏¡Ó, µ´÷ª”–◊Ó∫Û“ªÃıø…“‘ «‘§≤‚Œ™Ã¯◊™µƒ∑÷÷ß÷∏¡Ó, ‘§≤‚Œ™Ã¯◊™µƒ∑÷÷ß÷∏¡Óµƒ∫Û–¯÷∏¡ÓΩ´‘⁄œ¬“ª∏ˆ ±÷”÷Ð∆⁄Ω¯––¥¶¿Ì°£GS464E ¥¶¿Ì∆˜∫À≤…”√ 3 ∏ˆ ±÷”÷Ð∆⁄—”≥Ÿµƒ °∞»°÷∏ °™ ∑÷÷ß°± —≠ª∑µ¸¥˙…˺∆, µ⁄ 1 ∏ˆ ±÷”÷Ð∆⁄ ∏˘æð≥Öں∆ ˝∆˜ (program counter, PC) µƒ÷µ∑√Œ ÷∏¡Óª∫¥Ê µ⁄ 2 ∏ˆ ±÷”÷Ð∆⁄ ÷∏¡Óª∫¥Ê≤È—ØÕͱœ, »°≥ˆ◊Ó∂ý 8 Ãı÷∏¡Ó * µ⁄ 3 ∏ˆ ±÷”÷Ð∆⁄ ÷ÃıΩ‚Œˆ÷∏¡Ó, ‘§≤‚∑÷÷ß÷∏¡ÓµƒÃ¯◊™∑ΩœÚ∫Õï◊™ƒø±Í, »Áπ˚»°≥ˆµƒ∂ýÃı÷∏¡Ó÷–¥Ê‘⁄‘§≤‚Œ™Ã¯◊™µƒ∑÷÷ß÷∏¡Ó, ‘Ú–Ë“™∏˘æð¥À¿ý÷∏¡Ó÷–◊Ó‘Áµƒƒ«Ãı¿¥∏¸–¬ PC ÷µ ”…”⁄»°≥ˆ÷∏¡Ó≤¢‘§≤‚≥ˆ∫Û–¯÷∏¡Ó PC –Ë“™ª®∑— 3 ∏ˆ ±÷”÷Ð∆⁄, ∆‰÷–”– 2 ∏ˆ ±÷”÷Ð∆⁄ŒÞ∑®»∑±£ƒÐ»°≥ˆ”–“‚“µƒ÷∏¡Ó, Œ™±Ð√‚–‘ƒÐÀ ß, GS464E ¥¶¿Ì∆˜∫À µœ÷¡À∑÷÷߃ø±Íª∫≥Â∆˜ (BrBTB), ÷±Ω”∏˘æð»°÷∏À˘ π”√µƒ PC ÷µ‘§≤‚∫Û–¯÷∏¡Óµƒ PC ÷µ°£»Áπ˚»°≥ˆµƒ÷∏¡Ó÷–√ª”–‘§≤‚Œ™Ã¯◊™µƒ∑÷÷ß÷∏¡Ó, BrBTB “≤√ª”–‘§≤‚≥ˆ–Ë“™Ã¯±‰µƒ PC ÷µ, ‘Ú»°÷∏≤øº˛¥”µ±«∞ PC œÚ∫ÛÀ≥–Ú»°÷∏¡Ó°£BrBTB Œ™ 128 œÓ»´œý¡™Ω· ππ, π”√µ±«∞ ±÷”÷Ð∆⁄µƒ PC ÷µ¿¥À˜“˝œ¬∏ˆ ±÷”÷Ð∆⁄µƒ‘§≤‚ PC, ‘⁄∆‰‘§≤‚’˝»∑µƒ«Èøˆœ¬, º¥ π”––Ë“™Ã¯◊™µƒ∑÷÷ß÷∏¡Ó, »°÷∏¡˜ÀÆœþ“≤≤ªª·∂œ¡˜°£BrBTB µƒπ¶ƒÐ «∏˘æ𵱫∞ PC ¿¥‘§≤‚œ¬“ª∏ˆ ±÷”÷Ð∆⁄µƒ»°÷∏ PC, ”√”⁄œ˚≥˝∑÷÷ß÷∏¡Ó÷Æ∫Ûµƒ»°÷∏ø’≈ð, µ´ «∑÷÷ß‘§≤‚π§◊˜ªπ «–Ë“™Ω‚Œˆ≤ªÕ¨µƒ÷∏¡Ó¿¥Ω¯––≤ªÕ¨¥¶¿Ìµƒ°£ ∑÷÷ß÷∏¡Óï◊™∑ΩœÚµƒ‘§≤‚ π”√“ªÃ◊◊È∫œ∑÷÷ß¿˙ ∑±Ì (BHTs), ∞¸¿® 1 ∏ˆ 16384 œÓµƒ»´æ÷∑÷÷ß¿˙ ∑±Ì (global branch history table, GBHT), 1 ∏ˆ 16384 œÓµƒæ÷≤ø∑÷÷ß¿˙ ∑±Ì (local branch history table, LBHT) ∫Õ 1 ∏ˆ 16384 œÓµƒ»´æ÷—°‘Ò¿˙ ∑±Ì (global branch select table, GSEL)°£√ø∏ˆ ±÷”÷Ð∆⁄»°≥ˆµƒ◊Ó∂ý 8 Ãı÷∏¡Óø…“‘Õ¨ ±≤È’“’‚Ã◊∑÷÷ß¿˙ ∑±Ì£¨…œ ˆ 3 ∏ˆ∑÷÷ß¿˙ ∑±Ì÷–µƒ√øœÓ∂º « 2 bit ±•∫Õº∆ ˝∆˜, ∆‰◊Ó∏þ±»ÃÿŒª‘⁄ GBHT ∫Õ LBHT ÷–”√”⁄÷∏√˜Ã¯◊™∑ΩœÚ, ∂¯‘⁄ GSEL ÷–‘Ú”√”⁄æˆ∂®—°”√ GBHT ªπ « LBHT µƒ‘§≤‚∑ΩœÚ°£ º‰Ω”ï◊™÷∏¡ÓµƒÃ¯◊™ƒø±Í‘§≤‚∑÷Œ™¡Ω÷÷«Èøˆ: ∫Ø ˝∑µªÿï◊™÷∏¡Ó (MIPS ÷∏¡ÓºØ÷–µƒ JR r31 ÷∏¡Ó) ≤…”√ 16 œÓµƒ∑µªÿµÿ÷∑’ª (return address stack, RAS) Ω¯––‘§≤‚°£µ±∑÷÷ß‘§≤‚Ω◊∂Œ∑¢œ÷∫Ø ˝µ˜”√ï◊™÷∏¡Ó ±, Ω´∏√÷∏¡Ó—”≥Ÿ≤€÷Æ∫Û÷∏¡Óµƒ PC ÷µ—π»Î (push) ÷¡ RAS ÷–°£µ±∑÷÷ß‘§≤‚Ω◊∂Œ∑¢œ÷∫Ø ˝∑µªÿï◊™÷∏¡Ó ±, ‘ÚµØ≥ˆ (pop) RAS ’ª∂•À˘¥Ê∑≈µƒ PC ÷µ◊˜Œ™Ã¯◊™ƒø±Íµƒ‘§≤‚÷µ°£Œ™¡À∑¿÷π‘⁄¥ÌŒÛÕ∆≤‚¬∑æ∂…œ÷¥––∂‘ RAS ’ª∂•÷∏¡ÓªÚ’ª∂•ƒ⁄»ðµƒ¥ÌŒÛ–Þ∏ƒ, RAS µƒ’ª∂•÷∏’Î∫Õµ±«∞’ª∂•µƒ PC ÷µ∂º”–∆‰¡Ÿ ±±∏∑ð, ”√”⁄◊‘æ¿’˝ ≥˝…œ ˆ∫Ø ˝∑µªÿï◊™÷∏¡Ó÷ÆÕ‚µƒµƒº‰Ω”ï◊™÷∏¡Ó π”√œÓ ˝Œ™ 1024 µƒÃ¯◊™ƒø±Íª∫¥Ê∆˜ (jump branch target address cache, JBTAC) Ω¯––‘§≤‚, ∏√ª∫¥Ê∆˜ π”√»°÷∏ PC º∞ï◊™¿˙ ∑–≈œ¢Ω¯––À˜“˝°£ µ±÷∏¡Ó±ª»°≥ˆ∫Û, ª·∏˘æ𑧓άΖ≈œ¢µƒ÷∏ æ, ∞¥’’≤ªÕ¨µƒ÷∏¡Ó¿ý–Õ, ∑÷± π”√…œ ˆ 3 ÷÷ª˙÷∆÷–µƒƒ≥ “ª÷÷ª˙÷∆Ω¯––∑÷÷ß‘§≤‚. æ≠π˝∑÷÷ß‘§≤‚Ω◊∂Œ∫Û, ÷∏¡Ó±ª¥Ê»Î¥Û–°Œ™ 64 œÓµƒ÷∏¡Ó∂”¡–÷–. ‘⁄ GS464E ¥¶ ¿Ì∆˜∫À÷–, ª˘”⁄∏√÷∏¡Ó∂”¡–µƒ◊ ‘¥ªπ µœ÷¡À—≠ª∑ª∫≥Â∆˜ (loop buffer). —≠ª∑ª∫≥Â∆˜ª·ºý≤‚Ω¯»Î÷∏¡Ó∂”¡–µƒ÷∏¡Ó¡˜ PC Ãÿ’˜, µ±∑¢œ÷÷∏¡Ó¡˜÷–∞¸∫¨“ª∏ˆ≤ª¥Û”⁄ 56 Ãı÷∏¡Óµƒµ•≤„—≠ª∑ ±, Ω´Õ£÷π¥”÷∏¡Óª∫¥Ê»°÷∏, ∂¯ «÷±Ω”¥”÷∏¡Ó∂”¡–÷–»°≥ˆ÷∏¡ÓÀÕµΩ“Î¬ÎΩ◊∂Œ. µ±—≠ª∑¥Œ ˝¥ÔµΩ≤¢ÕÀ≥ˆ—≠ª∑ ±, —≠ª∑ª∫≥Â∆˜ª·±ª«Âø’. “άÎπ¶ƒÐ≤øº˛‘⁄√ø∏ˆ ±÷”÷Ð∆⁄ª·¥”÷∏¡Ó∂”¡–Õ∑≤ø»°≥ˆ 4 Ãı÷∏¡ÓΩ¯––“ά࣓άÎπ˝≥õƒ––Œ™ΩœºÚµ•, æÕ «Ω´÷∏¡Ó¬Î∑≠“ÎŒ™∑Ω±„π¶ƒÐ≤øº˛¥¶¿Ìµƒƒ⁄≤ø¬Î, ±Í ∂≥ˆ÷∏¡Ó¿ý–Õ°¢À˘–Ë“™≤Ÿ◊˜µƒºƒ¥Ê∆˜∫≈“‘º∞÷∏¡Ó¬Î÷–ø…ƒÐ∞¸∫¨µƒ¡¢º¥ ˝, ”√”⁄Ω”œ¬¿¥µƒºƒ¥Ê∆˜÷ÿ√¸√˚Ω◊∂Œ°£ 5.1.2 ÷∏¡Ó∑÷≈‰”ÎÃ·Ωªµ•‘™ ÷∏¡Ó∑÷≈‰”ÎÃ·Ωªµ•‘™∏∫‘÷∏¡Ó‘⁄¥¶¿Ì∆˜∫À÷–µƒ∑÷≈‰”Î∂®–Ú, æþÃÂ∞¸¿®ºƒ¥Ê∆˜÷ÿ√¸√˚£¨÷∏¡Ó∑÷≈‰£¨÷∏¡Ó∑¢…‰£¨÷∏¡Ó÷ÿ∂®–Ú£¨÷∏¡ÓÃ·Ωªº∞∑÷÷ߔΓÏ≥£¥¶¿Ì’‚º∏∏ˆπ¶ƒÐ°£ “άÎ∫Ûµƒ÷∏¡Ó ◊œ»Ω¯––ºƒ¥Ê∆˜÷ÿ√¸√˚, ÀÊ∫Û∏˘æð≤Ÿ◊˜¿ý–Õ∑÷≈‰÷¡≤ªÕ¨µƒ∑¢…‰∂”¡–÷–°£ºƒ¥Ê∆˜÷ÿ√¸√˚ «∂Ø衘ÀÆœþ÷–Ω¯––¬“–Ú∑¢…‰µƒπÿº¸ºº ı, Ω´Œ™÷∏¡Ó÷–÷∏∂®µƒ¬þº≠ºƒ¥Ê∆˜∏˜◊‘∑÷≈‰“ª∏ˆŒÔ¿Ìºƒ¥Ê∆˜°£‘⁄ GS464E ¥¶¿Ì∆˜∫À÷–, –Ë“™Ω¯––÷ÿ√¸√˚µƒºƒ¥Ê∆˜”–: Õ®”√∂®µ„ºƒ¥Ê∆˜°¢Õ®”√∏°µ„ºƒ¥Ê∆˜°¢HILO ºƒ¥Ê∆˜°¢DSP øÿ÷∆ºƒ¥Ê∆˜°¢∏°µ„±»ΩœΩ·π˚ºƒ¥Ê∆˜°£’‚–©–Ë“™÷ÿ√¸√˚µƒºƒ¥Ê∆˜∏˜◊‘Ω¯––”≥…‰, Õ®π˝ŒÔ¿Ìºƒ¥Ê∆˜”≥…‰±Ì (physical register map table, PRMT) ¿¥±£¥ÊŒÔ¿Ìºƒ¥Ê∆˜∫Õ¬þº≠ºƒ¥Ê∆˜÷ƺ‰µƒπÿœµ. ”√”⁄Õ®”√∂®µ„ºƒ¥Ê∆˜÷ÿ√¸√˚µƒŒ™ 128 œÓ 64Œªø̵ƒºƒ¥Ê∆˜∂—, ”√”⁄Õ®”√∏°µ„ºƒ¥Ê∆˜÷ÿ√¸√˚µƒŒ™ 128 œÓ 64Œªø̵ƒºƒ¥Ê∆˜∂—, ”√”⁄ HILO ºƒ¥Ê∆˜÷ÿ√¸√˚µƒŒ™ 16 œÓ 128Œªø̵ƒºƒ¥Ê∆˜∂—, ”√”⁄ DSP øÿ÷∆ºƒ¥Ê∆˜ ÷ÿ√¸√˚µƒŒ™ 32 œÓ 32Œªø̵ƒºƒ¥Ê∆˜∂—, ”√”⁄∏°µ„±»ΩœΩ·π˚ºƒ¥Ê∆˜÷ÿ√¸√˚µƒŒ™ 32 œÓ 32Œªø̵ƒºƒ¥Ê ∆˜∂—°£ GS464E ¥¶¿Ì∆˜∫À÷–”– 3 ∏ˆ∂¿¡¢µƒ∑¢…‰∂”¡–: 16 œÓµƒ∂®µ„∑¢…‰∂”¡–£¨∂®µ„∑¢…‰∂”¡–∏∫‘‘¥≤Ÿ◊˜ ˝∫Õƒø±Í≤Ÿ◊˜ ˝æ˘Œ™Õ®”√∂®µ„ºƒ¥Ê∆˜°¢HILO ºƒ¥Ê∆˜ªÚ DSP øÿ÷∆ºƒ¥Ê∆˜µƒ‘ÀÀ„÷∏¡Ó∫Õ∑÷÷ß÷∏¡Ó 24 œÓµƒ∏°µ„∑¢…‰∂”¡–£¨∏°µ„∑¢…‰∂”¡–∏∫‘‘¥≤Ÿ◊˜ ˝∫Õƒø±Í≤Ÿ◊˜ ˝æ˘Œ™Õ®”√∏°µ„ºƒ¥Ê∆˜ªÚ∏°µ„±»ΩœΩ·π˚ºƒ¥Ê∆˜µƒ‘ÀÀ„÷∏¡Ó∫Õ∑÷÷ß÷∏¡Ó * 32 œÓµƒ∑√¥Ê∑¢…‰∂”¡–£¨∑√¥Ê∑¢…‰∂”¡–≥˝¡À∏∫‘À˘”–∂®µ„£¨∏°µ„µƒ∑√¥Ê≤Ÿ◊˜÷∏¡ÓÕ‚, ªπ∞¸¿®øÿ÷∆ºƒ¥Ê∆˜≤Ÿ◊˜÷∏¡Ó (CP0 ÷∏¡Ó) “‘º∞‘⁄∂®µ„”Î∏°µ„ºƒ¥Ê∆˜º‰Ωªª• ˝æðµƒ÷∏¡Ó ¥”øÿ÷∆π¶∫ƒµƒΩ«∂»≥ˆ∑¢, 3 ∏ˆ∑¢…‰∂”¡–æ˘≤…”√“∆∂Ø÷∏’Î∂¯∑«“∆∂Ø∂”¡–÷–¥Ê¥¢ƒ⁄»ðµƒπпÌ≤þ¬‘, √ø ∏ˆ ±÷”÷Ð∆⁄–Ë“™º∆À„µ±«∞”¶µ±∑¢…‰÷∏¡Óµƒ÷∏’ΰ£÷ª”–‘¥ºƒ¥Ê∆˜∂º“—æ≠æÕ–˜µƒ÷∏¡Ó≤≈ƒÐ±ª∑¢…‰, ∂¯÷∏¡Ó‘⁄ºƒ¥Ê∆˜÷ÿ√¸√˚Ω◊∂Œ ±æÕª·œ»ºÏ≤È∆‰‘¥ºƒ¥Ê∆˜ «∑Ò“—æ≠æÕ–˜°£»Ù∆‰‘¥≤Ÿ◊˜ ˝ªπ√ª”–◊º±∏∫√, ‘Ú∏√÷∏¡Ó‘⁄Ω¯––÷∏¡Ó∑÷≈‰“‘º∞‘⁄∑¢…‰∂”¡–÷–µƒ ±∫Ú, ∂º“™Ω´◊‘…̵ƒ‘¥ºƒ¥Ê∆˜∫≈Õ¨Ω·π˚◊ÐœþªÚ«∞¿°◊Ðœþµƒƒø±Íºƒ¥Ê∆˜∫≈œýª•±»Ωœ, “‘»∑∂®±æÃı÷∏¡ÓÀ˘–˵ƒ‘¥ºƒ¥Ê∆˜ «∑ÒæÕ–˜°£¥À ±À˘ π”√µƒºƒ¥Ê∆˜∫≈∂º «æ≠π˝ºƒ¥Ê∆˜÷ÿ√¸√˚∫ÛµƒŒÔ¿Ìºƒ¥Ê∆˜∫≈°£…œ ˆµƒ 3 ∏ˆ∑¢…‰∂”¡–∂º≤…”√¬“–Ú∑¢…‰ª˙÷∆, ÷∏¡ÓµƒÀ˘”–‘¥≤Ÿ◊˜ ˝÷ª“™◊º±∏∫√æÕø…“‘∑¢…‰°£µ±¥Ê‘⁄∂ý∏ˆ∑¢…‰∫Ú—° ±, ◊Ó‘ÁΩ¯»Îµƒ÷∏¡Óæþ”–◊Ó∏þµƒ”≈œ»º∂°£ ‘⁄ GS464E ¥¶¿Ì∆˜∫À÷–, ÷∏¡Ó±ªÀ≥–ړάÎ∫Õ÷ÿ√¸√˚£¨¬“–Ú∑¢…‰∫Õ÷¥––, µ´ «“™”––ÚÃ·Ωª°£÷ÿ∂®–Ú∂”¡–∏∫‘÷∏¡Óµƒ”––ÚΩ· ¯, À¸¥”ºƒ¥Ê∆˜÷ÿ√¸√˚ƒ£øȪһ°≥ÖÚ÷∏¡Ó–Ú–≈œ¢, ≤¢”––Úµÿ±£¥Ê¡˜ÀÆœþ÷–À˘”–“—æ≠ÕÍ≥…ºƒ¥Ê∆˜÷ÿ√¸√˚µ´Œ¥Ã·Ωªµƒ÷∏¡Ó°£÷∏¡Ó‘⁄π¶ƒÐµ•‘™÷¥––Õͱœ≤¢–¥ªÿ (writeback) ∫Û, ÷ÿ∂®–Ú∂”¡–∞¥’’≥ÖÚ÷∏¡Ó–ÚÀ≥–ÚÃ·Ωª’‚–©÷∏¡Ó°£÷ÿ∂®–Ú∂”¡–◊Ó∂ýø…Õ¨ ±»ðƒ… 128 Ãı÷∏¡Ó°£÷ÿ∂®–Ú∂”¡–√ø∏ˆ ±÷”÷Ð∆⁄◊Ó∂ýø…“‘Ã·Ωª∂”¡–∂•∂Àµƒ 4 Ãı“—æ≠¥¶”⁄–¥ªÿ◊¥Ã¨µƒ÷∏¡Ó°£÷∏¡ÓµƒÃ·Ωª–≈œ¢ª·ÀÕÕ˘ºƒ¥Ê∆˜÷ÿ√¸√˚ƒ£øÈ, ”√”⁄–Þ∏ƒ÷ÿ√¸√˚µƒ◊¥Ã¨, Õ¨ ±ªπ–Ë“™Õ®÷™∑√¥Ê÷ÿ∂®–Ú∂”¡–, “ÚŒ™¥Ê¥¢÷∏¡Ó–Ë“™Ã·Ωª∫Û≤≈ƒÐ–Þ∏ƒ¥Ê¥¢∆˜µƒƒ⁄»ð°£GS464E ¥¶¿Ì∆˜∫À µœ÷¡Àæ´»∑“Ï≥£, µ±»°÷∏¡Ó£¨“άΪÚ÷¥–– ±∑¢…˙“Ï≥£ ±, “Ï≥£–≈œ¢±ªÀÕ÷¡÷ÿ∂®–Ú∂”¡–±£¥Êœ¬¿¥, ÷ª”–“Ï≥£÷∏¡Ó≥…Œ™÷ÿ∂®–Ú∂”¡–Õ∑ ±, ≤≈Ω¯––“Ï≥£±®∏ʔΥ¶¿Ì°£”≤º˛Ω¯––µƒ“Ï≥£¥¶¿Ìπ§◊˜∞¸¿®: Ω´“Ï≥£‘≠“Ú°¢“Ï≥£÷∏¡Óµƒ PC ÷µµ»–≈œ¢º«¬ºµΩ”–πÿµƒ CP0 ºƒ¥Ê∆˜÷–, ≤¢∏˘æð“Ï≥£¿ý–Õ∞—“Ï≥£¥¶¿Ì≥Öڵƒ»Îø⁄µÿ÷∑ÀÕµΩ≥Öں∆ ˝∆˜÷–°£ ∑÷÷ß÷∏¡Ó‘⁄ºƒ¥Ê∆˜÷ÿ√¸√˚∫ÛΩ¯»Î÷ÿ∂®–Ú∂”¡–∫Õ∑¢…‰∂”¡–µƒÕ¨ ±ªπª·À≥–ÚµÿΩ¯»Î∑÷÷ß÷∏¡Ó∂”¡–°£GS464E ¥¶¿Ì∆˜∫À÷–µƒ∑÷÷ß÷∏¡Ó∂”¡–◊Ó∂ýø…“‘»ðƒ… 24 Ãı∑÷÷ß÷∏¡Ó, ∏√∂”¡–ª·º«¬º∑÷÷ß÷∏¡ÓΩ¯––∑÷÷ß‘§≤‚ ±µƒ‘§≤‚Ω·π˚°£∑÷÷ß÷∏¡Ó∫Õ∆‰À˚÷∏¡Ó“ª—˘∂º–Ë“™‘⁄π¶ƒÐ≤øº˛÷¥––, µ´ «∆‰Ω·π˚◊Ðœþ∂ÓÕ‚∞¸∫¨∑÷÷ßΩ·π˚, ∑÷÷ßΩ·π˚ª·–¥ªÿµΩ∑÷÷ß÷∏¡Ó∂”¡–°£’‚–©Ω·π˚∞¸¿® JR ∫Õ JALR ÷∏¡Óµƒƒø±Íµÿ÷∑, “‘º∞Ãıº˛◊™“∆÷∏¡Óµƒ◊™“∆∑ΩœÚ, ¿˚”√’‚–©Ω·π˚ø…“‘≈–∂œ’‚Ãı÷∏¡Óµƒ∑÷÷ß‘§≤‚ «∑Ò◊º»∑. ≤ª¬€‘§≤‚≥…π¶”Î∑Ò, ∑÷÷ß÷∏¡Óµƒ÷¥––Ω·π˚∂ºª·∑¥¿°µΩ»°÷∏≤øº˛, ”√”⁄–Þ’˝œýπÿµƒ∑÷÷ß‘§≤‚∆˜, “‘∞Ô÷˙∫Û–¯∑÷÷ß÷∏¡Óµƒ‘§≤‚°£‘§≤‚¥ÌŒÛµƒ∑÷÷ß÷∏¡Ó∫Õ‘⁄À¸÷Æ∫Û»°Ω¯¿¥µƒ÷∏¡Ó∂º–Ë“™»°œ˚°£∑÷÷ß÷∏¡Ó∂”¡–∏∫‘∑¢ÀÕ∑÷÷ߥ̌ۻ°œ˚◊Ðœþ, ∏˘æð∂”¡–÷–º«¬ºµƒ≥ÖÚ÷∏¡Ó–Ú, ◊º»∑µÿΩ¯––∑÷÷ß»°œ˚≤Ÿ◊˜, Õ¨ ±Ω´’˝»∑µƒ PC ÷µÀÕµΩ≥Öں∆ ˝ ∆˜÷–°£ 5.1.3 ∂®µ„µ•‘™∫Õ∏°µ„µ•‘™ GS464E ¥¶¿Ì∆˜∫À÷–µƒ∂®µ„µ•‘™∞¸∫¨ 1 ∏ˆ∂ý∂Àø⁄∂®µ„ºƒ¥Ê∆˜∂—“‘º∞ 2 ∏ˆÕÍ»´œýÕ¨µƒ∂®µ„‘ÀÀ„µ•‘™°£∂®µ„ºƒ¥Ê∆˜∂—π≤ 128 œÓ, “ªπ≤”– 8 ∏ˆ∂¡∂Àø⁄∫Õ 4 ∏ˆ–¥∂Àø⁄°£√øÃı∂®µ„‘ÀÀ„¡˜ÀÆœþ÷–æ˘∞¸∫¨: ”√”⁄ ÷¥––∂®µ„º”°¢ºı°¢±»Ωœ°¢œð⁄Â÷∏¡ÓµƒÀ„ ı¬þº≠µ•‘™ (arithmetic logic unit, ALU), ”√”⁄÷¥––“∆Œª°¢—≠ª∑ “∆Œª∫Õ±»Ãÿ÷»°”ÎΩÿ∂œ÷∏¡Óµƒ—≠ª∑Õ∞–Œ“∆Œª∆˜, Œª≤Ÿ◊˜µ•‘™, «∞µº¡„º∆ ˝∆˜, ∑÷÷ߥ¶¿Ìµ•‘™, ≥˝∑®≤øº˛∫Õ≥À∑®∆˜, √ø÷÷‘ÀÀ„µ•‘™µƒ ˝¡øæ˘Œ™ 1 ∏ˆ°£À˘”–∆µ∑±÷¥––µƒ÷∏¡Óæ˘‘⁄ 1 ∏ˆ ±÷”÷Ð∆⁄ƒ⁄÷¥––Õͱœ, «“Õ®π˝º§Ω¯µƒ«∞¿°ª˙÷∆…˺∆, πµ√¥Ê‘⁄ºƒ¥Ê∆˜œýπÿµƒ∂ýÃı÷∏¡Óø…“‘±≥øø±≥¡¨–¯∑¢…‰°£≥À∑®∆˜≤…”√»´¡˜Àƅ˺∆, ø…Ω¯–– 64x64”–∑˚∫≈ªÚŒÞ∑˚∫≈≥À∑®‘ÀÀ„, ‘ÀÀ„—”≥ŸŒ™ 3 ∏ˆ ±÷”÷Ð∆⁄, »´¡˜Àƅ˺∆ πµ√√ø∏ˆ≥À∑®∆˜‘⁄√ø∏ˆ ±÷”÷Ð∆⁄∂ºø…Ω” Ð 1 Ãı–¬µƒ÷∏¡Ó, ≤¢≤˙…˙ 128±»Ãÿµƒ≥Àª˝Ω·π˚°£ GS464E ¥¶¿Ì∆˜∫À÷–µƒ∏°µ„≤øº˛∞¸∫¨ 1 ∏ˆ∂ý∂Àø⁄∏°µ„ºƒ¥Ê∆˜∂—“‘º∞ 2 ∏ˆÕÍ»´œýÕ¨µƒ∏°µ„‘ÀÀ„µ•‘™°£∏°µ„∂ý∂Àø⁄ºƒ¥Ê∆˜∂—π≤ 128 œÓ, “ªπ≤”– 8 ∏ˆ∂¡∂Àø⁄∫Õ 4 ∏ˆ–¥∂Àø⁄°£√øÃı∏°µ„‘ÀÀ„¡˜ÀÆœþ÷–æ˘∞¸∫¨: ∏Ò Ω◊™ªªµ•‘™ (”√”⁄÷¥–– °∞∂®µ„◊™Œ™∏°µ„°±£¨°∞µ•æ´∂»∏°µ„◊™Œ™À´æ´∂»∏°µ„°± ’‚¿ý∏Ò Ω◊™ªª÷∏¡Ó), ∏°µ„±»Ωœµ•‘™, ∏°µ„≥˝∑®µ•‘™, ∏°µ„ø™∑Ω”Î«Ûµπ ˝µ•‘™, “‘º∞∏°µ„≥Àº” (fused multiply®Cadd) µ•‘™ (”√”⁄÷¥––∏°µ„º”°¢ºı°¢≥À°¢≥Àº”°¢≥Àºı÷∏¡Ó), √ø÷÷‘ÀÀ„µ•‘™µƒ ˝¡øæ˘Œ™ 1 ∏ˆ°£∆‰÷–∏Ò Ω◊™ªªµ•‘™≤…”√ 3 º∂»´¡˜Àƅ˺∆, ∏°µ„≥Àº”µ•‘™≤…”√ 4 º∂»´¡˜Àƅ˺∆°£ 5.1.4 ∑√¥Êµ•‘™ ∑√¥Ê≤øº˛∞¸∫¨“‘œ¬µƒ◊”≤øº˛: ∑√¥Ê÷∏¡Ó∑¢…‰∂”¡– mmqueue£¨∑√¥Ê◊®”√∂®µ„ºƒ¥Ê∆˜∂— mr£¨¡Ω∏ˆ∑√¥Êµÿ÷∑…˙≥…≤øº˛ memaddr, “ªº∂ ˝æðª∫¥Ê£¨“ªº∂ ˝æð TLB £¨¡Ω ∏ˆ∑√¥Ê±Í«©±»Ωœ≤øº˛ dtagcmp°¢∑√¥Ê÷ÿ∂®–Ú∂”¡– cp0queue, “‘º∞∂˛º∂ TLB ≤øº˛ sec tlb°£÷ª”–“ª∑ðµƒ◊”≤øº˛”…¡ΩÃı∑√¥Ê¡˜ÀÆœþπ≤œÌ π”√°£œ¬Õº’π æ¡À∑√¥Êµ•‘™¡˜ÀÆœþ£∫ |

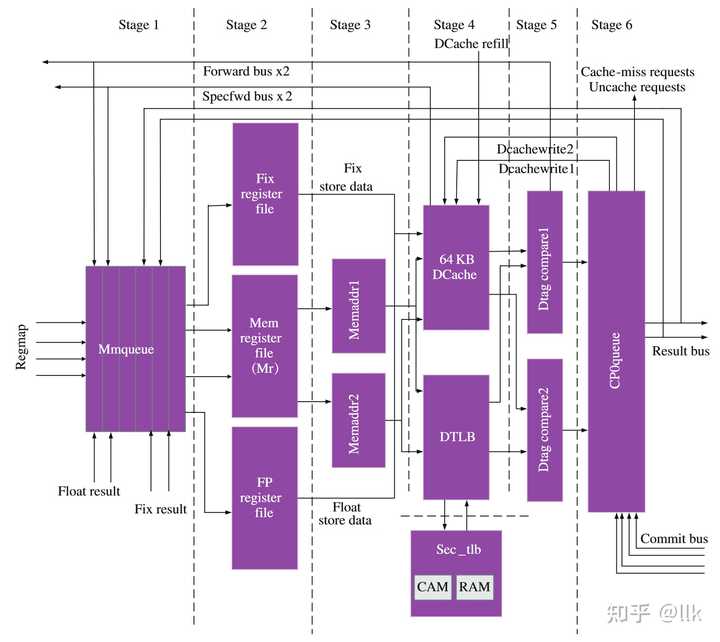

|

|

∑√¥Ê÷∏¡Ó∑¢…‰∂”¡– mmqueue Ω” ’ºƒ¥Ê∆˜÷ÿ√¸√˚≤øº˛ÀÕ¿¥µƒ÷∏¡Ó–≈œ¢, ≤¢Ω´µ±«∞“—æ≠æÕ–˜«“ ≥ÖÚ÷∏¡Ó–Ú…œ◊Ó¿œµƒ∑√¥Ê÷∏¡Ó∑¢…‰µΩ∑√¥Ê¡˜ÀÆœþ…œ°£¥Û≤ø∑÷∑√¥Ê÷∏¡Ó∂ºø…“‘‘⁄¡Ω∏ˆ∑√¥Ê≤øº˛÷–µƒ»Œ“‚“ª∏ˆ÷¥––, ¥Ê¥¢≤Ÿ◊˜∫Õº”‘ÿ≤Ÿ◊˜“ª—˘, ª·µ»¥˝µÿ÷∑∫Õ ˝æðÕ¨ ±æÕ–˜∫Û, ≤≈∑¢…‰µΩ¡˜ÀÆœþ÷–°£¡ΩÃı∑√¥Ê¡˜ÀÆœþ‘⁄”µ”– 4 ∏ˆ∂¡∂Àø⁄µƒºƒ¥Ê∆˜∂— mr ÷–∂¡»°À˘–˵ƒ≤Ÿ◊˜ ˝; “ª–©Ãÿ ‚÷∏¡Ó–Ë“™∑¢ÀÕ∂ÓÕ‚«Î«Û»•∂®µ„≤øº˛ªÚ∏°µ„≤øº˛, “‘ªÒ»°À˘–˵ƒ‘¥ ˝æð, ¿˝»Á, ∏°µ„¥Ê¥¢÷∏¡Ó SDC1 À˘–Ë“™¥Ê¥¢µƒ ˝æð÷ª¥Ê∑≈‘⁄∏°µ„ºƒ¥Ê∆˜∂—÷–°£À˘”–¿ý–Õµƒ∑√¥Ê÷∏¡Óµƒµÿ÷∑øœ∂®ª·¥Ê∑≈‘⁄ mr ÷–, ≤ª–Ë“™¥”∂®µ„≤øº˛ªÚ∏°µ„≤øº˛»°°£¡ΩÃı∑√¥Ê¡˜ÀÆœþ∑÷±”µ”–“ª∏ˆµÿ÷∑º∆À„ƒ£øÈ memaddr£¨µÿ÷∑º∆À„ƒ£øÈ∏˘æð∑√¥Ê÷∏¡Óµƒ¿ý–Õ, ¿˚”√ mr ∂¡≥ˆµƒºƒ¥Ê∆˜ƒ⁄»ðº∆À„∑√¥Ê÷∏¡Óµƒ–ȃ‚µÿ÷∑ (effective address, EA ªÚ–ȵÿ÷∑)°£–ȵÿ÷∑µÕŒªÀÕµΩ ˝æðª∫¥Êƒ£øÈΩ¯––À˜“˝≤È’“, ’˚∏ˆ–ȵÿ÷∑ÀÕµΩ DTLB ƒ£øÈΩ¯–––È µµÿ÷∑∑≠“ΰ£ “ªº∂ ˝æðª∫¥Ê «”… 4 ¬∑◊Èœý¡™°¢√ø“ª¬∑ 16 KB ¥Û–°µƒÀ´∂Àø⁄Àʪ˙¥Ê¥¢∆˜ (random access memory, RAM) ππ≥…µƒ, ¡Ω∏ˆ∂Àø⁄∑÷±∂‘”¶“ªÃı∑√¥Ê¡˜ÀÆœþ°£√ø∏ˆ∂Àø⁄∏˘æðµÿ÷∑µƒµÕŒª∂¡»° RAM ÷–¥Ê∑≈µƒ±Í«©∫Õ ˝æð, ≤¢Ω´∂¡≥ˆµƒΩ·π˚ÀÕ÷¡ dtagcmp ≤øº˛◊º±∏Ω¯––±Í«©±»Ωœ°£Õ¨ ±, ¥Ê¥¢÷∏¡Ó–Ë“™¥Ê¥¢µƒ ˝æð‘⁄¥Àµ•‘™º∆À„, Õ¨—˘“≤ÀÕµΩ dtagcmp ≤øº˛°£“ªº∂ ˝æð TLB ”Γªº∂ ˝æðª∫¥ÊÕ¨ ±±ª≤È—Ø°£“ªº∂ ˝æð TLB ≤øº˛ π”√ 2 ∏ˆ 64±»Ãÿ–ȵÿ÷∑◊˜Œ™ ‰»Î, ≤È—ØÀ´∂Àø⁄µƒ»´œý¡™◊È÷صƒ DTLB, µ√µΩ 2 Ãı∑√¥Ê÷∏¡Óµƒ–ȵÿ÷∑À˘∂‘”¶µƒ 48±»ÃÿŒÔ¿Ìµÿ÷∑ (physical address, PA ªÚ µµÿ÷∑), ≤¢ÀÕ÷¡ dtagcmp ƒ£øÈ◊º±∏Ω¯––±Í«©±»Ωœ°£¥ÀÕ‚, ¥Û≤ø∑÷ CP0 œýπÿµƒÃÿ»®÷∏¡Ó, »Á MTC0 º∞ MFC0 ∂º «‘⁄ DTLB ƒ£øÈ÷¥––µƒ°£¡Ω∏ˆ µµÿ÷∑±»Ωœƒ£øÈ dtagcmp ƒ£øÈ∑÷±∂‘”¶“ªÃı∑√¥Ê¡˜ÀÆœþ°£’‚∏ˆƒ£øÈΩ´ ˝æðª∫¥Êƒ£øÈ∂¡≥ˆµƒ 4 ¬∑±Í«©”Î DTLB ƒ£øȵ√µΩµƒ µµÿ÷∑Ω¯––±»Ωœ, »∑∂®“ªº∂ ˝æðª∫¥Ê «∑Ò√¸÷–, “‘º∞√¸÷–‘⁄ƒƒ“ª¬∑°£√¸÷–¬∑µƒ ˝æ𪷱ª»°≥ˆ, ∫Õ ˝æðÀÕ¿¥µƒ ¥Ê¥¢÷∏¡ÓÀ˘“™¥Ê¥¢µƒ ˝æð“ª∆º∆À„, µ√µΩ∑√¥Ê÷∏¡Óµƒ÷¥––Ω·π˚, ≤¢ÀÕµΩ∑√¥Ê÷ÿ∂®–Ú∂”¡– cp0queue°£∑√¥Ê÷ÿ∂®–Ú∂”¡– cp0queue Ω” ’≥ÖÚ÷∏¡Ó–Ú–≈œ¢, Ω” ’ dtagcmp ƒ£øÈÀÕ¿¥µƒ÷∏¡Óµÿ÷∑”Î ˝æð–≈ œ¢, ≤¢Õ®π˝ªÿπˆª˙÷∆¿¥Œ¨ª§¬“–Ú∑¢…‰µƒ∑√¥Ê÷∏¡Ó÷ƺ‰µƒ’˝»∑÷¥–––Ú°£Cp0queue ≥˝¡À∑√¥Ê÷∏¡Ó÷ÿ∂®–Úπ§◊˜÷ÆÕ‚, ‘⁄√ø∏ˆ ±÷”÷Ð∆⁄ªπ–Ë“™–¥ªÿ◊Ó∂ý 2 Ãıø…–¥ªÿµƒ º”‘ÿ÷∏¡Ó∫Õ ◊Ó∂ý 2 Ãıø…–¥ªÿµƒ¥Ê¥¢÷∏¡Ó£¨Ω´◊Ó∂ý 1 Ãı∑√¥Ê ß–ßµƒ÷∏¡ÓÀÕÕ˘ª∫¥Ê ß–ß∂”¡–£¨Ω´◊Ó∂ý 2 Ãı“—æ≠Ã·Ωª «“±ª‘ –Ì–¥“ªº∂ ˝æðª∫¥Êµƒ¥Ê¥¢÷∏¡Ó∑¢ÀÕµΩ“ªº∂ ˝æðª∫¥Êµƒ–¥∂Àø⁄°£Cp0queue ø…“‘±ª ”◊˜∑√¥Ê÷∏¡ÓµƒπÈÀÞ, À˘”–∑√¥Ê÷∏¡Ó∂º‘⁄’‚¿ÔΩ¯––ª∫¥Ê ߖߥ¶¿Ì∫Õ–¥ªÿ°£ƒø±Íºƒ¥Ê∆˜Œ™∂®µ„ºƒ¥Ê∆˜µƒº”‘ÿ¿ý–Õ∑√¥Ê÷∏¡Ó‘⁄¥” ˝æðª∫¥Ê¡˜Àƺ∂µΩ dtagcmp ¡˜Àƺ∂¥´µð ±, ª·Ω¯––≤¬≤‚÷«∞∑¥¿°≤Ÿ◊˜, ≥∆Œ™ specfwd°£‘⁄¥” dtagcmp ¡˜Àƺ∂µΩ cp0queue ¥´µð ±, ª·÷ÿ–¬∑¢ÀÕ…œ“ª ∏ˆ ±÷”÷Ð∆⁄µƒ specfwd –≈œ¢, –Œ≥… fwdbus ◊Ðœþ°£¡ΩÃı∑√¥Ê◊Ðœþµƒ◊Ó∂ý 4 Ãı”√”⁄÷«∞∑¥¿°µƒ–≈œ¢ª·±ª ÀÕ÷¡∂®µ„∑¢…‰∂”¡–∫Õ∑√¥Ê∑¢…‰∂”¡–, ≤¢÷√≤¬≤‚æÕ–˜±Íº«, πµ√÷∏¡Óø…“‘≤¬≤‚µÿ∑¢…‰°£»Áπ˚≤¬≤‚«∞¿°≤¬≤‚¥ÌŒÛ, ‘Úª·∑¢ÀÕ∂‘”¶∏√∑√¥Ê¡˜ÀÆœþµƒ≤¬≤‚»°œ˚–≈∫≈ spec cancel, ≤¬≤‚¥ÌŒÛµƒÃıº˛∞¸¿®: “ªº∂ ˝æðª∫¥ÊŒ¥√¸÷–£¨ªÚ’þ“ªº∂ DTLB Œ¥√¸÷–£¨ªÚ’þ∏√÷∏¡Ó‘⁄ cp0queue ±ªªÿπˆ°£≤¬≤‚»°œ˚–≈∫≈Ω´ª·»°œ˚∂‘”¶µƒ specfwd “‘º∞ fwdbus ◊Ðœþ¥¯¿¥µƒÀ˘”–∫Ûπ˚, “—æ≠≤¬≤‚∑¢…‰µƒœý”¶÷∏¡Ó“≤ª·±ª»°œ˚, ≤¢ªÿµΩ∑¢…‰∂”¡–÷ÿ–¬µ»¥˝∑¢…‰ª˙ª·°£‘⁄…œ ˆ «∞¿°ª˙÷∆µƒ◊˜”√œ¬, ø…“‘µ√÷™∑√¥Ê÷∏¡Ó‘⁄¿ÌœÎ«Èøˆœ¬µƒ—”≥Ÿ: ∑√¥Ê÷∏¡ÓµΩ∂®µ„÷∏¡Ó“‘º∞∑√¥Ê÷∏¡ÓµΩ∑√¥Ê÷∏¡Óµƒ load-to-use —”≥ŸŒ™ 4 ∏ˆ ±÷”÷Ð∆⁄, ∑√¥Ê÷∏¡ÓµΩ∏°µ„÷∏¡Óµƒ load-to-use —”≥Ÿ Œ™ 6 ∏ˆ ±÷”÷Ð∆⁄°£ ∑√¥Ê÷ÿ∂®–Úª˙÷∆ «”√”⁄Œ¨ª§¬“–Ú∑¢…‰µƒ∑√¥Ê÷∏¡Ó÷ƺ‰÷¥––À≥–Úµƒª˙÷∆°£‘⁄÷Æ«∞µƒ GS464 ¥¶¿Ì∆˜∫À…˺∆÷–, ∑√¥Ê÷ÿ∂®–Ú≤…»°µƒ « ˝æ𥴵ðª˙÷∆, π”√ ˝æ𥴵ðª˙÷∆Ω¯––∑√¥Ê÷∏¡Ó÷ÿ∂®–Úµƒ∑Ω∑®Œ™: µ±“ªÃı÷∏¡Óæ≠π˝∑¢…‰¬∑æ∂µΩ¥Ô÷ÿ∂®–Ú∂”¡– ±, ’‚Ãı÷∏¡Ó–Ë“™¥”À˘”–÷¥–––Ú‘⁄À¸÷Æ«∞µƒ£¨”Î∆‰œýπÿµƒ¥Ê¥¢÷∏¡Ó¥¶ªÒ»°∂‘”¶ ˝æð; Õ¨ ±, »Áπ˚’‚Ãı÷∏¡Ó «¥Ê¥¢÷∏¡Ó, ƒ«√¥’‚Ãı÷∏¡Óªπ“™Ω´À¸◊‘º∫µƒ ˝æ𥴵ð∏¯À˘”–µƒ“—æ≠‘⁄÷ÿ∂®–Ú∂”¡–÷–”Î∆‰œýπÿµƒ«“÷¥–––Ú‘⁄À¸∫Û√ʵƒ÷∏¡Ó°£ºÚµ•Àµ¿¥, ∏√ª˙÷∆ø…“‘√Ë ˆ≥… °∞»°«∞∏¯∫Û°±°£‘⁄ŒÔ¿Ì…˺∆…œ, µœ÷’‚—˘µƒ ˝æ𥴵ðª˙÷∆¥˙º€∫Ð¥Û: ∏√÷∏¡Óø…ƒÐ¥”∂ýÃı÷∏¡Ó¥¶»°µ√ ˝æð, ø…ƒÐ¥”»Œ“‚÷∏¡Ó¥¶ƒ√»°»Œ“‚◊÷Ω⁄µƒ ˝æð; ¥Ê¥¢÷∏¡Óø…ƒÐ∞—◊‘º∫µƒ ˝æ𥴵ð∏¯∂ýÃı÷∏¡Ó, ø…ƒÐΩ´ ˝æ𥴵ð∏¯»Œ“‚÷∏¡Óµƒ»Œ“‚◊÷Ω⁄Œª÷√°£’‚∏ˆª˙÷∆µƒŒÔ¿Ì…˺∆π˝”⁄∏¥‘”, —œ÷ÿœÞ÷∆¡À∂”¡–µƒπʃ£, ÷¬ π GS464 ¥¶¿Ì∆˜∫À÷–µƒ∑√¥Ê÷ÿ∂®–Ú∂”¡–÷ª”– 24 œÓ¥Û–°°£ ‘⁄ GS464E ¥¶¿Ì∆˜∫À÷– µœ÷¡À 2 ∏ˆ∑√¥Êπ¶ƒÐµ•‘™, Õ¨“ª ±øÃø…ƒÐ”– 2 Ãı÷∏¡ÓΩ¯»Î∑√¥Ê÷ÿ∂®–Ú∂”¡–, ˝æ𥴵ðª˙÷∆µƒ µœ÷¥˙º€∏¸ «ƒ—“‘Ω” а£Œ™¡À÷∏þ÷∏¡Ó≤¢––∂»£¨Ω´∑√¥Ê÷ÿ∂®–Ú∂”¡–œÓ ˝‘ˆ¥Û, ‘⁄ GS464E ¥¶¿Ì∆˜∫À÷–, ÷ª±£¡Ù¡À÷∏¡Ó «∑Òœýπÿµƒ≈–∂œ, »°œ˚¡À ˝æ𥴵ðµƒπ¶ƒÐ, Õ®π˝÷∏¡ÓªÿπˆµΩ∑¢…‰∂”¡–÷ÿ–¬∑¢…‰µƒª˙÷∆¿¥±£÷§÷¥––µƒ’˝»∑–‘°£∆‰æþÃÂ≤Ÿ◊˜∑Ω Ω»Áœ¬À˘ ˆ: µ±“ªÃı÷∏¡Óæ≠π˝∑¢…‰¬∑æ∂µΩ¥Ô÷ÿ∂®–Ú∂”¡– ±, ∑¢œ÷∂”¡–÷–”–÷¥–––Ú‘⁄À¸÷Æ«∞µƒ”Î∆‰œýπÿµƒ¥Ê¥¢÷∏¡Ó, ƒ«√¥∏√÷∏¡ÓªÿπˆµΩ∑√¥Ê∑¢…‰∂”¡– mmqueue, ≤¢µ»¥˝∏√¥Ê¥¢÷∏¡Ó–¥»Î“ªº∂ ˝æð ª∫¥Ê∫Û‘Ÿ¥Œ∑¢…‰; »Áπ˚“ªÃı¥Ê¥¢÷∏¡Óæ≠π˝∑¢…‰¬∑æ∂µΩ¥Ô÷ÿ∂®–Ú∂”¡– ±, ∑¢œ÷∂”¡–÷–“—”–÷¥–––Ú‘⁄À¸÷Æ∫Ûµƒ”Î∆‰œýπÿµƒ÷∏¡Ó, ƒ«√¥Ω´’‚–©÷∏¡ÓªÿπˆµΩ mmqueue, »√’‚–©÷∏¡Ó÷ÿ–¬∑¢…‰°£∆‰÷–, ÷∏¡Óœýπÿµƒ≈–∂œª·∏˘æð÷∏¡Óµƒ≤Ÿ◊˜¿ý–Õ£¨∑√¥Êµÿ÷∑µ»–≈œ¢Ω¯––æ´»∑µƒ≈–∂œ, ¿˝»Á, ∂‘ A µÿ÷∑µƒ∞Î◊÷¥Ê¥¢ SH ≤Ÿ◊˜≤¢≤ªª· πµ√∂‘ A+2 µÿ÷∑µƒ∞Î◊÷»° LH ≤Ÿ◊˜ªÿπˆ°£ºÚµ•Àµ¿¥, ∏√ª˙÷∆ø…“‘√Ë ˆŒ™ °∞µ»«∞¥Ú∫Û°±°£Õ®π˝≤…»° °∞µ»«∞¥Ú∫Û°± µƒ∑√¥Ê÷ÿ∂®–Ú≤þ¬‘¿¥¥˙ÃÊ °∞»°«∞∏¯∫Û°± µƒ≤þ¬‘, ¬‘‘ˆº”¡À∑¢…‰∂”¡–∫Õ∑√¥Ê÷ÿ∂®–Ú∂”¡–µƒ…˺∆∏¥‘”∂», ‘⁄“ª–©«Èøˆœ¬ª·¥¯¿¥…Ÿ–Ì–‘ƒÐΩµµÕ, µ´ «»¥¥Û¥ÛΩµµÕ¡ÀŒÔ¿Ì…˺∆µƒƒ—∂», ø…“‘‘⁄Õ¨—˘µƒ…˺∆÷˜∆µœ¬ π”√∏¸¥Ûµƒ∑√¥Ê÷ÿ∂®–Ú∂”¡–, ‘ˆº”∑√¥Ê÷∏¡Ó≤¢––∂», ø…“‘∏¸∫√µƒ»ð»Ã∑√¥Ê—”≥Ÿ°£Õ¨ ±, “≤Œ™÷ß≥÷∏¸¥Ûµƒ∑√¥ÊøÌ∂», »Á 256±»ÃÿœÚ¡ø∑√¥Ê÷∏¡Ó, ÷π©¡Àø…ƒÐ–‘°£ GS464E ¥¶¿Ì∆˜∫À÷–µƒ“ªº∂ ˝æðª∫¥Ê≤…»° 4 ¬∑◊Èœý¡™Ω·ππ, ◊Ð¥Û–°Œ™ 64 KB°£∆‰÷–, √ø“ª¬∑¥Û–°Œ™ 16 KB, ∑÷Œ™ 256 ∏ˆª∫¥Ê––, √ø“ª––Œ™ 64 ◊÷Ω⁄°£“ªº∂ ˝æðª∫¥Ê π”√–ȵÿ÷∑À˜“˝, µµÿ÷∑±Í ∂, √ø“ª∏ˆª∫¥Ê–––Ë“™ 48±»Ãÿµƒ±Í«©¿¥¥Ê¥¢ µµÿ÷∑–≈œ¢, “‘º∞ 512±»Ãÿµƒ ˝æ𿥥ʥ¢ ˝æð, ±Í«©∫Õ ˝æð≤ø∑÷∂º π”√ ECC –£—Ȭο¥Ω¯––»þ”ý±£ª§°£“ªº∂ ˝æðª∫¥Ê≤…”√ LRU Ãʪª≤þ¬‘, µ±“ª∏ˆª∫¥Ê––±ª≤È—Ø√¸÷– ±, ªÚ“Úª∫¥Ê ß–ß∂¯±ª–¬ÃӻΠ±, ª·±ªµ˜’˚µΩ◊Óƒ—±ªÃʪªµƒ”≈œ»º∂; »Áπ˚“ª∏ˆª∫¥Ê––“Ú∂ý∫À“ª÷¬–‘µº÷¬µƒÕ‚≤ø«Î«Û±ªŒÞ–ß, ∏√ª∫¥Ê––ª·±ªµ˜’˚÷¡◊Ó»ð“◊±ªÃʪªµƒ”≈œ»º∂°£“ªº∂ ˝æðª∫¥Ê «“ª∏ˆÀ´∂Àø⁄µƒª∫¥ÊΩ·ππ, √ø“ª∏ˆ ±øÃ◊Ó∂ýø…“‘ µœ÷ 2 Ãı∑√¥Ê÷∏¡Óµƒ≤È—Ø≤Ÿ◊˜£ªÕ¨ ±, ¥Ê¥¢÷∏¡Ó¥”∑√¥Ê÷ÿ∂®–Ú∂”¡–∑¢≥ˆ–¥ª∫¥Ê≤Ÿ◊˜ ±, “≤Õ®π˝’‚ 2 ∏ˆ∂Àø⁄Ω¯–––¥≤Ÿ◊˜, ∆‰”≈œ»º∂µÕ”⁄∑√¥Ê÷∏¡Óµƒ≤È—Ø≤Ÿ◊˜°£≥˝¥À÷ÆÕ‚, ECC –£—È≥ˆ¥Ì ±µƒ◊‘æ¿’˝≤Ÿ◊˜∫Õª∫¥Ê ß–ß÷ÿÃӫΫÛ∂º–Ë“™¥”µ⁄“ª∏ˆ–¥∂Àø⁄Ω¯–––¥»Î, –¥»Î≤Ÿ◊˜Ω´∞¥’’Ãÿ∂®”≈œ»º∂Ω¯––, ≤¢∂‘µÕ”≈œ»º∂µƒ≤Ÿ◊˜≤˙…˙◊Ë»˚°£ –È µµÿ÷∑∑≠“Îπ§◊˜‘⁄”≤º˛ µœ÷…œ «”…¡Ωº∂ TLB ¿¥ÕÍ≥…µƒ°£“ªº∂ ˝æð TLB ∂‘»Ìº˛Õ∏√˜, √ø¥Œ∑√¥Ê≤Ÿ◊˜÷¥–– ±±ª≤È—Ø; »Ìº˛ø…º˚µƒ «∂˛º∂ TLB, »Ìº˛–Þ∏ƒ TLB µƒ÷∏¡Ó (»Á TLBWR) ª·÷±Ω”–Þ∏ƒ∂˛º∂ TLB°£ ∂˛º∂ TLB ∂‘“ªº∂ ˝æð TLB «∞¸∫¨πÿœµ, “ªº∂ ˝æð TLB µƒ»± ߪ·◊‘∂Ø¥”∂˛º∂ TLB ÷–≤È’“≤¢»° ªÿ, ”≤º˛ª·◊‘∂ØŒ¨ª§∞¸∫¨πÿœµ°£ ¥ÀÕ‚, ÷∏¡Ó TLB “≤ «∏˘æð∂˛º∂ TLB ÷–µƒƒ⁄»ðÃӻεƒ°£ “ªº∂ ˝æð TLB µƒπʃ£Œ™ 32 œÓ, ∂˛º∂ TLB ‘Ú «”… 2 ∏ˆ≤ø∑÷◊È≥…, ∞¸¿® 64 œÓ»´œý¡™µƒø…±‰“≥¥Û–°µƒµÿ÷∑ø…—∞÷∑¥Ê¥¢∆˜ (content addressable memory, CAM) ≤ø∑÷, “‘º∞ 8 ¬∑◊Èœý¡™£¨√ø“ª¬∑ 128 œÓ, π≤º∆ 1024 œÓµƒπÃ∂®“≥¥Û–°µƒ RAM ≤ø∑÷, ’‚¡Ωº∂ TLB ÷–µƒ√ø“ªœÓ∂ºø…“‘◊∞‘ÿ 1 ∏ˆ±Í◊º MIPS À´“≥°£“ª º∂ ˝æð TLB «À´∂Àø⁄µƒ, ∑÷±∂‘”¶”⁄ 2 ∏ˆ∑√¥Êπ¶ƒÐ≤øº˛, “ªº∂ TLB ≤È—Ø∑¢…˙≤ª√¸÷– ±, ª·—°‘Ò‘⁄≥ÖÚ÷∏¡Ó–Ú…œΩœ¿œµƒƒ«Ãı÷∏¡Ó¿¥≤È—Ø÷ª”– 1 ∏ˆ∂Àø⁄µƒ∂˛º∂ TLB°£∂˛º∂ TLB ≤È—Ø–Ë“™ª®∑— 2 ∏ˆ ±÷”÷Ð∆⁄, »Áπ˚√¸÷–, ƒ«√¥√¸÷–µƒΩ·π˚ª·–¥»Î“ªº∂ ˝æð TLB, ∆‰Ãʪª≤þ¬‘Œ™Àʪ˙Ãʪª; »Áπ˚Œ¥√¸÷–, ∆‰Ω·π˚“≤ª·Õ®÷™∑√¥Ê÷ÿ∂®–Ú∂”¡–°£–Ë“™≤È—Ø∂˛º∂ TLB µƒ÷∏¡Óæ≠π˝∑√¥Ê÷ÿ∂®–Ú∂”¡–÷–µƒªÿπˆª˙÷∆, ÷ÿ–¬ªÿµΩ∑¢…‰∂”¡–, ‘Ÿ¥Œ∑¢…‰ ±, ∂˛º∂ TLB µƒ≤È—ØΩ·π˚“—æ≠∑µªÿ, “Ú¥Àø…“‘≈–∂œ «∑Ò’Ê’˝µƒ∑¢…˙¡À TLB ß–ß“Ï≥£°£ ∂˛º∂ TLB ÷–ø…±‰“≥≤ø∑÷ (CAM ≤ø∑÷) ∫ÕπÃ∂®“≥≤ø∑÷ (RAM ≤ø∑÷) ª·±ªÕ¨ ±≤È—Ø, µ´ «»Ìº˛Ω¯–– TLB –¥»Î ±, ÷ª”–∆‰÷–“ª∏ˆª·±ª–Þ∏ƒ: »Áπ˚–¥»ÎœÓµƒ“≥¥Û–°”Î÷«∞≈‰÷√∫√µƒπÃ∂®“≥œýÕ¨, ‘Ú TLB ÷∏¡Ó ª·Ω´ TLB ±ÌœÓ–¥»ÎπÃ∂®“≥≤ø∑÷, ∑Ò‘Ú, Ω´–¥»Îø…±‰“≥≤ø∑÷°£ 64 œÓµƒ CAM ≤ø∑÷∫Õ 8 ¬∑◊Èœý¡™µƒ RAM ≤ø∑÷∂º≤…”√Àʪ˙Ãʪª≤þ¬‘°£ GS464E ¥¶¿Ì∆˜∫Àµƒ“ªº∂ ˝æðª∫¥Ê «“ª∏ˆ–¥ªÿ (writeback) Ωµƒª∫¥Ê, À˘”–µƒ¥Ê¥¢≤Ÿ◊˜∂º–Ë“™∂‘“ªº∂ ˝æðª∫¥ÊΩ¯–––¥»Î°£ µ±¥Ê¥¢÷∏¡Ó∑¢…˙ª∫¥Ê ß–ß ±, –Ë“™Ω´¥Ê¥¢÷∏¡ÓÀ˘–˵ƒª∫¥Ê––¥”ƒ⁄¥Ê∞·‘À÷¡“ªº∂ ˝æðª∫¥Ê, ‘ŸΩ¯–––¥»Î°£»ª∂¯‘⁄∫Ð∂ý«Èøˆœ¬, ¥Ê¥¢÷∏¡Ó∂º«„œÚ”⁄ÃÓ¬˙’˚∏ˆª∫¥Ê––, “Ú¥À’‚∏ˆ∞·‘Àπ˝≥ÃæÕœ‘µ√∂ý”ý, ªπ¥¯¿¥¡À≤ª…Ÿµƒ ±º‰”Îπ¶∫ƒø™œ˙°£ Œ™¡ÀΩµµÕ’‚∏ˆø™œ˙, GS464E ¥¶¿Ì∆˜∫À÷–“˝»Î¡À¥Ê¥¢ÃÓ≥‰ (store fill) ª˙÷∆°£∏√ª˙÷∆µƒπ§◊˜‘≠¿ÌŒ™: µ±¥Ê¥¢÷∏¡Ó‘⁄“ªº∂ ˝æðª∫¥Ê÷–∑¢…˙ª∫¥Ê ß–ß ±, ∆‰∑√¥Ê ߖ߫Ϋ۪·Ω´¥˝¥Ê¥¢µƒ ˝æð“ª≤¢ÀÕ÷¡Œª”⁄ª∫¥Ê ß–ß∂”¡–÷–µƒ¥Ê¥¢ÃÓ≥‰ª∫≥«¯, Õ¨ ±, ∏√∑√¥Ê ߖ߫Ϋۑðª∫∑√Œ SCache°£»Áπ˚Ω”œ¬¿¥µƒ∂ýÃı¥Ê¥¢«Î«Û‘⁄∏√ª∫≥«¯÷–≥…π¶µÿ∆¥¬˙¡Àª∫¥Ê––, ƒ«√¥÷ª–ËœÚ SCache «Î«Ûø’∞◊µƒª∫¥Ê––º¥ø…°£ ’µΩø’∞◊––«Î«Ûµƒ SCache ≤ªª·∑√Œ ƒ⁄¥Ê, ‘⁄Ω¯––∂ý∫À“ª÷¬–‘¥¶¿Ì∫Û÷±Ω”∑µªÿ, ª∫¥Ê ß–ß∂”¡–∏∫‘Ω´ª∫≥«¯÷–∆¥¬˙µƒ ˝æð÷ÿÃÓªÿ“ªº∂ ˝æðª∫¥Ê°£‘⁄¥Ê¥¢ÃÓ≥‰Ω¯––∆⁄º‰, œý”¶µƒ¥Ê¥¢÷∏¡Óø…“‘ÕÀ≥ˆ¡˜ÀÆœþ, Õ∑≈∂”¡–ø’º‰°£»Áπ˚Ωœ≥§ ±º‰√ª”–∆¥¬˙“ª∏ˆª∫¥Ê––, ªÚ”ˆµΩ¡À Ù”⁄Õ¨“ª∏ˆª∫¥Ê––µƒº”‘ÿ≤Ÿ◊˜, ªÚ”ˆµΩƒ⁄¥Ê∆¡’œ¿ý≤Ÿ◊˜ (»Á SYNC ªÚ CACHE ÷∏¡Ó), ¥Ê¥¢ÃÓ≥‰ª˙÷∆æÕª·Ω¯––ÕÀ≥ˆ¥¶¿Ì, œÚ SCache «Î«Û“ª∏ˆ’˝≥£µƒª∫¥Ê––, ¥˝Ω·π˚∑µªÿ∫Û, ‘⁄ª∫≥«¯Ω¯–– ˝æð∆¥¥’≤Ÿ◊˜, Ω´∆¥¥’∫ÛµƒΩ·π˚ÃÓªÿ“ªº∂ ˝æðª∫¥Ê°£ ”≤º˛ª·º«¬º¥Ê¥¢ÃÓ≥‰≥…π¶”Î∑ÒµƒΩ¸∆⁄¿˙ ∑, ≤¢∂‘¥Ê¥¢ÃÓ≥‰ª˙÷∆Ω¯––◊‘∂ص˜’˚°£ GS464E ¥¶¿Ì∆˜∫À÷– µœ÷µƒ¥Ê¥¢ÃÓ≥‰ª˙÷∆ø…“‘ ”√”⁄∂ý∫À¥¶¿Ì∆˜µƒ«Èøˆ, ºı…Ÿ¡À¥Ê¥¢÷∏¡Óµº÷¬µƒƒ⁄¥Ê∂¡»°, ≤¢‘ –̥ʥ¢÷∏¡Ó÷«∞ÕÀ≥ˆ¡˜ÀÆœþ, ÷…˝¡À¥¶¿Ì∆˜µƒ’˚ÃÂ÷¥–––‘ƒÐ°£ 5.1.5 ª∫¥Ê ß–ß∂”¡– ª∫¥Ê ß–ß∂”¡–Œª”⁄“ªº∂ª∫¥Ê”Î SCache ÷ƺ‰, ∏∫‘∂‘ Victim Cache Ω¯––∑√Œ ∫ÕπпÌ, µœ÷ª∫¥Ê ߖ߫Ϋ۵ƒ¥¶¿Ì∫Õ÷ÿÃÓπ§◊˜, ≤¢∏∫‘”≤º˛‘§»°«Î«Ûµƒ…˙≥…∫Õ¥¶¿Ì°£ ‘⁄ GS464E ¥¶¿Ì∆˜…˺∆÷–, ∂‘ª∫¥Ê ß–ßµƒ¥¶¿Ìπ˝≥ÃΩ¯––¡À∂ýœÓ¥¥–¬–‘µƒ∏ƒ∂Ø, ∞¸¿®ª˘”⁄ª∫¥Ê ß–ß∂”¡–µƒŒÞŒ€»æ”≤º˛‘§»°“˝«Ê…˺∆“‘º∞ø…“‘÷ß≥÷∂ý∫À«Èøˆµƒ¥Ê¥¢ÃÓ≥‰ª˙÷∆°£ ª∫¥Ê ß–ß∂”¡–π≤”– 16 œÓ, Ω¯»Î∏√∂”¡–µƒ«Î«Û∞¸¿®∑√¥Ê÷ÿ∂®–Ú∂”¡–∑¢¿¥µƒ∑√¥Ê ߖ߫Ϋ۰¢»°÷∏≤øº˛∑¢¿¥µƒ÷∏¡Ó ߖ߫Ϋۓ‘º∞ SCache ∑¢¿¥µƒ∂ý∫À“ª÷¬–‘«Î«Û, ¥ÀÕ‚, ”≤º˛‘§»°“˝«Êª·Ω´…˙≥…µƒ ˝æð∫Õ÷∏¡Ó‘§»°«Î«Û“≤ÀÕ∏¯ª∫¥Ê ß–ß∂”¡–, ”…∏√∂”¡–Ω¯––¥¶¿Ì°£À˘”–Ω¯∂”«Î«Ûµƒµÿ÷∑æ˘Œ™ µµÿ÷∑°£ª∫¥Ê ß–ß∂”¡–÷–µƒª∫¥Ê ߖ߫Ϋ۪·œ»≤È—Ø Victim Cache, »Áπ˚√¸÷–, ‘Úª·Ω´Ω·π˚÷ÿÃÓªÿ“ªº∂ª∫¥Ê, ≤¢Ω´“ªº∂ª∫¥ÊÃʪª≥ˆµƒª∫¥Ê––ÃӻΠVictim Cache ÷–÷Æ«∞±ª»°≥ˆµƒŒª÷√; »Áπ˚ Victim Cache ≤È—ØŒ¥√¸÷–, ‘Úª·∑√Œ SCache, ¥˝ SCache µƒΩ·π˚∑µªÿ∫Û, ÃӻΓªº∂ª∫¥Ê, Ω´“ªº∂ª∫¥ÊÃʪª≥ˆµƒ”––ß ˝æð∏˘æð LRU À„∑®–¥»Î Victim Cache, ≤¢Ω´ Victim Cache Ãʪª≥ˆµƒ”––ß‘ý ˝æ𖥪ÿµΩ SCache°£ ª∫¥Ê ߖ߫ΫÛ◊Ð «ª·œ»≤È—Ø Victim Cache, ≤È—ØŒ¥√¸÷– ±‘Ÿ≤È—Ø SCache, ’‚÷÷¥Æ––∑√Œ µƒ…˺∆ΩµµÕ¡Àª∫¥Ê“ª÷¬–‘Œ¨ª§µƒ∏¥‘”∂»°£ª∫¥Ê ß–ß∂”¡–÷–”… SCache ∑¢¿¥µƒ∂ý∫À“ª÷¬–‘«Î«Ûª·∂‘“ªº∂ª∫¥Ê∫Õ Victim Cache Ω¯––≤È—Ø, ∏˘æð≤È—ØΩ·π˚∫Õ“ª÷¬–‘«Î«Ûµƒ¿ý–Õ, ∂‘ª∫¥Ê––Ω¯––ŒÞ–ß°¢–¥ªÿµ»≤Ÿ◊˜, ≤¢Ω´Ω·π˚∑µªÿ SCache°£ª∫¥Ê ß–ß∂”¡–÷–µƒ”≤º˛‘§»°«Î«Ûª·∂‘ SCache Ω¯––≤È—Ø, ∏˘æð≤È—ØΩ·π˚, Ω´‘§»°¿¥µƒ ˝æð‘ð¥Ê‘⁄∂”¡–÷–°£»Áπ˚”–ª∫¥Ê ߖ߫ΫÛ∫Õ”≤º˛‘§»°«Î«Û≤Ÿ◊˜Õ¨“ª∏ˆª∫¥Ê––, ƒ«√¥‘§»°µΩµƒ ˝æðª·∑¢ÀÕ∏¯’‚∏ˆª∫¥Ê ߖ߫Ϋ۰£ª∫¥Ê ß–ß∂”¡–ª·∂®∆⁄«Â≥˝µÙƒ«–©“ª÷±√ª”–±ª π”√µΩµƒ‘§»° ˝æð°£’‚—˘µƒ‘§»°¥¶¿Ì∑Ω Ω≤ªª·¥¯¿¥»Œ∫Œ“ªº∂ª∫¥ÊŒ€»æ°£«Î«ÛÕ¨“ª∏ˆª∫¥Ê––µƒª∫¥Ê ß–ß≤Ÿ◊˜ª·‘⁄ª∫¥Ê ß–ß∂”¡–÷–Ω¯––∫œ≤¢, µ´÷ªœÞ”⁄Õ¨ Ù”⁄ ˝æðª∫¥Ê ߖߪÚ÷∏¡Óª∫¥Ê ß–ß°£ª∫¥Ê ß–ß∂”¡–ªπ”–◊®√≈µƒª∫≥«¯”√”⁄¥Ê¥¢∑√¥Ê ߖߥʥ¢÷∏¡Óµƒ ˝æð, “‘÷ß≥÷¥Ê¥¢ÃÓ≥‰ª˙÷∆°£ GS464E ¥¶¿Ì∆˜∫À÷– π”√¡À◊Ó∂ýÕ¨ ±÷ß≥÷ 4 ∏ˆ ˝æð∑√Œ ¡˜∫Õ 1 ∏ˆ÷∏¡Ó∑√Œ ¡˜µƒ¡˜ Ω”≤º˛‘§»°“˝«Ê, ˝æð∫Õ÷∏¡Óµƒ‘§»°œý∂‘∂¿¡¢°£ ∆‰÷–, ˝æð¡˜ Ω‘§»°“˝«Êø…“‘÷ß≥÷…˝–Ú∫ÕΩµ–Úƒ£ Ω, π”√∑√¥Ê ߖ߫Ϋۿ¥Ω®¡¢∫ÕŒ¨ª§∑√Œ ¡˜–≈œ¢; ∂¯÷∏¡Ó‘§»°÷ªƒÐ÷ß≥÷…˝–Úµƒ‘§»°, π”√÷∏¡Ó ߖ߫Ϋۿ¥Ω®¡¢∫ÕŒ¨ª§¡˜–≈ œ¢°£ µ± ߖ߫Ϋی™¡¨–¯µƒ 2 ∏ˆª∫¥Ê–– ±, Ω´ª·Ω®¡¢∑√Œ ¡˜, √ø∏ˆ∑√Œ ¡˜∂º≈‰”– 3±»Ãÿµƒµπ ˝º∆ ˝∆˜, ”√”⁄º∆À„’‚∏ˆ∑√Œ ¡˜ «∑Ò“—π˝∆⁄°£ª∫¥Ê ߖ߫ΫۻÁπ˚‘⁄ƒ≥∏ˆ∑√Œ ¡˜…œ—”–¯, ƒ«√¥≈‰ Ù”⁄’‚∏ˆ∑√Œ ¡˜µƒº∆ ˝∆˜ª·À¢–¬µΩ◊Ó¥Û÷µ°£∑√Œ ¡˜Ω®¡¢∫Û, æÕø…“‘¥•∑¢‘§»°, ‘§»°«Î«Ûµƒ¥•∑¢∞¸¿®œ¬¡–¡Ω÷÷«Èøˆ. »Áπ˚ª∫¥Ê ߖ߫Ϋۑ⁄ª∫¥Ê ß–ß∂”¡–÷–∫Õ‘§»°«Î«Û∫œ≤¢, ÷§√˜‘§»° «”–“ʵƒ, Ω´ª·∏˘æð¥À¥Œ ß–ßµƒµÿ÷∑≤È—Ø‘§»°“˝«Ê÷–“—æ≠Ω®¡¢µƒ∑√Œ ¡˜–≈œ¢°£÷∏¡Ó ߖ߫Ϋ۪·≤È—Ø÷∏¡Ó‘§»°“˝«Ê, ∂¯∑√¥Ê ߖ߫Ϋ۪·≤È—Ø ˝æ𑧻°“˝«Ê°£»Áπ˚∑√Œ ¡˜≤È—Ø√¸÷–, ‘Ú∏˘æð∑√Œ ¡˜µƒ…˝–ÚªÚΩµ–Ú–≈œ¢, ≤˙…˙ 1 ∏ˆ‘§»°«Î«Û, ‘§»°«Î«Ûµƒµÿ÷∑ « ß–ßµÿ÷∑º”…œÃÿ∂®‘ˆ¡ø; »Áπ˚∑√Œ ¡˜≤È—Ø≤ª√¸÷–, ‘Ú—∞’“º∆ ˝∆˜Œ™¡„ªÚº∆ ˝∆˜◊Ó–°µƒ∑√Œ ¡˜, Ω´∆‰∂•ÃÊ°£»Áπ˚Œ¥ƒÐ∫Õ‘§»°«Î«Û∫œ≤¢µƒª∫¥Ê ߖ߫Ϋۑ⁄ Victim Cache ÷–≤È—ØŒ¥√¸÷–, ‘Ú÷§√˜–Ë“™Ω¯––‘§»°, ¥À ±ª·∏˘æð¥À¥Œ ß–ßµƒµÿ÷∑≤È—Ø‘§»°“˝«Ê÷–µƒ∑√Œ ¡˜–≈œ¢, »Áπ˚∑√Œ ¡˜–≈œ¢≤È—Ø√¸÷–, ‘Ú∏˘æð∑√Œ ¡˜µƒ…˝–ÚªÚΩµ–Ú–≈œ¢, ≤˙…˙‘§»°«Î«Û, ‘§»°«Î«Ûµÿ÷∑ « ß–ßµÿ÷∑º”…œÃÿ∂®‘ˆ¡ø; ∑√Œ ¡˜≤È—ØŒ¥√¸÷–‘Ú≤ªΩ¯––≤Ÿ◊˜°£√ø¥Œ¥•∑¢‘§»° ±, ‘§»°µÿ÷∑œý∂‘”⁄ ß–ßµÿ÷∑µƒ‘ˆ¡øª·ÀÊ◊≈’‚∏ˆ∑√Œ ¡˜µƒ¿˙ ∑¥•∑¢¥Œ ˝∂¯±‰ªØ, ±ª¥•∑¢π˝µƒ¥Œ ˝‘Ω∂ý, ∆‰‘§»°‘ˆ¡ø‘Ω¥Û°£’‚∏ˆ‘ˆ¡ø÷µµƒ…œœÞ‘Ú”…“—Ω®¡¢µƒ∑√Œ ¡˜µƒ∏ˆ ˝æˆ∂®: µ±÷ª”– 1 ∏ˆ∑√Œ ¡˜¥Ê‘⁄ ±, ‘ˆ¡ø…œœÞ±ª…Ë∂®Œ™ 4 ∏ˆª∫¥Ê––¥Û–°; µ±≥¨π˝ 1 ∏ˆ∑√Œ ¡˜ ±, ∏√‘ˆ¡ø±ª…Ë∂®Œ™ 2 ∏ˆª∫¥Ê––¥Û–°£¨÷∏¡Ó‘§»°µƒ‘ˆ¡ø…œœÞ“ª÷±…Ë∂®Œ™ 4 ∏ˆª∫¥Ê––°£GS464E ¥¶¿Ì∆˜∫À π”√‘ˆ¡ø‘§»°≤þ¬‘, œý∂‘”⁄√ø¥Œ¥•∑¢æÕ‘§»°∂ýÃıµƒ≤þ¬‘, ‘⁄∑√Œ ¡˜‘§≤‚’˝»∑µƒ«Èøˆœ¬–ßπ˚ «œýÕ¨µƒ, µ´ «∑√Œ ¡˜‘§≤‚¥ÌŒÛ ±, ‘ˆ¡ø‘§»°≤þ¬‘ª·…Ÿ“ª–©ŒÞ–ßµƒ‘§»°«Î«Û°£ ª∫¥Ê GS464E ¥¶¿Ì∆˜∫À π”√¡À»˝º∂∆¨…œª∫¥ÊΩ·ππ, ∆‰÷–Œª”⁄√ø∏ˆ¥¶¿Ì∆˜∫Àƒ⁄≤øµƒÀΩ”–ª∫¥Ê∞¸¿®“ªº∂ ˝æðª∫¥Ê∫Õ“ªº∂÷∏¡Óª∫¥Ê, “‘º∞ ˝æð∫Õ÷∏¡Óπ≤”√µƒ Victim Cache, µ⁄»˝º∂ª∫¥ÊŒ™ SCache, ”…À˘”–¥¶¿Ì∆˜∫Àπ≤œÌ°£“ªº∂÷∏¡Óª∫¥ÊŒ™ 4 ¬∑◊Èœý¡™…˺∆, 64 KB »ð¡ø, ª∫¥Ê––¥Û–°64 ◊÷Ω⁄, Àʪ˙Ãʪª°£“ªº∂ ˝æðª∫¥Ê≤…”√ LRU Ãʪª≤þ¬‘£¨4 ¬∑◊Èœý¡™…˺∆, 64 KB »ð¡ø, ª∫¥Ê––¥Û–°64 ◊÷Ω⁄°£ Victim Cache ”ΡΩ∏ˆ“ªº∂ª∫¥Ê «exclusiveπÿœµ, ¥¶”⁄“ªº∂ª∫¥Ê÷–µƒª∫¥Ê––±ÿ∂®≤ª¥Ê‘⁄”⁄ Victim Cache ÷–; Victim Cache ”Î SCache Œ¨ª§∞¸∫¨ (inclusive) πÿœµ, “≤º¥¥¶”⁄ Victim Cache ÷–µƒª∫¥Ê––±ÿ∂®‘⁄ SCache ÷–”–∆‰∂‘”¶µƒ±∏∑𰣓ªº∂ª∫¥Ê∫Õ SCache «Inclusiveπÿœµ°£ Victim Cache Œ™ 16 ¬∑◊Èœý¡™, √ø“ª¬∑ 16 KB, π≤º∆ 256 KB, ª∫¥Ê––¥Û–°Œ™ 64 ◊÷Ω⁄, π”√ LRU Ãʪª≤þ¬‘°£Victim Cache Œª”⁄“ªº∂ª∫¥Ê÷Æœ¬, ”…ª∫¥Ê ß–ß∂”¡–Ω¯––πпÌ, µ±“ªº∂ª∫¥Ê∑¢…˙ª∫¥Ê ß–ß ±±ª≤È—Ø°£ ≤È—Ø Victim Cache ±, œ»∂¡»°±Í«©‘Ÿ∂¡»°√¸÷–¬∑µƒ ˝æðµƒ∑Ω Ω, π”√…Ÿ¡ø—”≥Ÿ¿¥ªª»°π¶∫ƒµƒΩµµÕ°£ ‘⁄ª∫¥Ê ߖ߫ΫÛ≤È—Ø Victim Cache Œ¥√¸÷–«Èøˆœ¬, ”…ª∫¥Ê ß–ß∂”¡–∏∫‘œÚ SCache ∑¢≥ˆ ߖ߫ΫÛ. µ±“ª∏ˆª∫¥Ê––¥”“ªº∂ª∫¥Ê÷–Ãʪª≥ˆ¿¥ ±, ª·±ªÃӻΠVictim Cache, ∂¯ Victim Cache Ãʪª≥ˆµƒ ˝æðΩ´ª·–¥ªÿµΩ SCache°£ ÷∏¡Óª∫¥Ê––”Î ˝æðª∫¥Ê––∂ºø…“‘¥Ê∑≈‘⁄ Victim Cache ÷–, “‘ª∫¥Ê––±Í«©”Ú÷–µƒ“ª∏ˆ∂ÓÕ‚±»Ãÿ¿¥◊ˆ«¯∑÷°£ SCache Œ™∆¨…œƒ©º∂ª∫¥Ê, ”…À˘”–¥¶¿Ì∆˜∫Àπ≤œÌ, “ª∏ˆÀƒ∫À¥¶¿Ì∆˜æÕª·”µ”– 4 ∏ˆ SCache “‘ π© 4 ∏ˆ¥¶¿Ì∆˜∫À π”√°£√ø∏ˆ SCache Œ™ 16 ¬∑◊Èœý¡™, »ð¡øŒ™ 1 MB, ª∫¥Ê––¥Û–°Œ™ 64 ◊÷Ω⁄, π”√ LRU ÃʪªÀ„∑®°£ √ø∏ˆ SCache π”√¥Û–°Œ™ 16 œÓµƒπпÌ∂”¡–¿¥≤È—Ø∫ÕŒ¨ª§. œý±»”⁄“ªº∂ª∫¥Ê∫Õ Victim Cache, √ø∏ˆ SCache µƒª∫¥Ê––ªπ∂ÓÕ‚∞¸∫¨ 64±»Ãÿµƒƒø¬º”Ú, ”√”⁄º«¬º∏√ ª∫¥Ê––±ªƒƒ∏ˆ¥¶¿Ì∆˜∫À≥÷”–, “‘º∞±ª¥¶¿Ì∆˜∫À≥÷”–µƒ «÷∏¡Ó––ªπ « ˝æð––°£‘⁄’‚∏ˆƒø¬ºµƒ…˺∆πʃ£œ¬, ◊Ó∂ý÷ß≥÷“ª∏ˆ–æ∆¨ºØ≥… 32 ∏ˆ¥¶¿Ì∆˜∫À. ‘⁄«¯∑÷ ˝æð––∫Õ÷∏¡Ó––÷ÆÕ‚, SCache ≤¢≤ª«¯∑÷“ªº∂ª∫¥Ê∫Õ Victim Cache, “Ú¥À“ªº∂ ˝æðª∫¥Ê≥÷”–µƒª∫¥Ê––ªÚ Victim Cache ≥÷”–µƒ ˝æðª∫¥Ê––∂ºª·±ª ”◊˜∏√¥¶¿Ì∆˜∫À≥÷”– ˝æðª∫¥Ê––°£‘⁄ GS464E ¥¶¿Ì∆˜∫À≈‰ Ùµƒ SCache ÷–, º”»Î¡Àª˘”⁄ª∫¥Ê“ª÷¬–‘µƒ”≤º˛øπ±√˚…˺∆°£µ±≥Ã–Ú π”√µƒ“≥µƒ¥Û–°±»“ªº∂ª∫¥Ê÷–√ø∏ˆª∫¥Ê¬∑µƒ»ð¡ø∏¸–°µƒ«Èøˆœ¬, æÕª·≥ˆœ÷±√˚µƒ«Èøˆ, Õ¨“ª∏ˆŒÔ¿Ìµÿ÷∑ª·±ª∑≈÷√‘⁄“ªº∂ª∫¥Ê÷–µƒ∂ý∏ˆÀ˜“˝…œ°£Œ™¡À±£÷§”≥…‰µΩÕ¨“ª∏ˆŒÔ¿Ìµÿ÷∑µƒ∂ý∏ˆ–ȵÿ÷∑÷ƺ‰µƒ ˝æð «“ª÷¬µƒ, SCache ‘⁄±Í«©”Ú÷–º”»Î¡À∂ÓÕ‚µƒ 2±»Ãÿµƒ“≥»æ…´”Ú, ¿˚”√ SCache ∂‘∆¨ƒ⁄¡Ωº∂ª∫¥Êµƒ∞¸∫¨πÿœµ, ±£÷§’‚∏ˆª∫¥Ê––÷ªƒÐ¥Ê‘⁄”⁄¬˙◊„µ±«∞“≥»æ…´”ÚµƒÃÿ∂®À˜“˝Œª÷√…œ°£µ±“ª∏ˆ∑√¥Ê«Î«Û“™«Û“≥»æ…´”Úµƒ¡Ì“ª∏ˆ÷µ ±, ª·∑¢…˙ª∫¥Ê ß–ß, SCache ∑¢œ÷∏√«Î«Û“≥»æ…´≤ª√¸÷–÷Æ∫Û, ª·Õ®π˝“ª÷¬–‘«Î«Û, –¥ªÿ≤¢ŒÞ–ߥ¶”⁄“ªº∂ª∫¥ÊªÚ Victim Cache ÷Æ÷–µƒª∫¥Ê––±∏∑ð, –Þ∏ƒ“≥»æ…´”Úµƒ÷µŒ™–¬÷µ∫Û, ‘Ÿ––∑µªÿ, “‘¥À±£÷§√ø∏ˆŒÔ¿Ìµÿ÷∑÷ª∂‘”¶“ª∏ˆ µ¿˝°£ª˘”⁄ª∫¥Ê“ª÷¬–‘µƒ”≤º˛øπ±√˚…˺∆ « GS464E ¥¶¿Ì∆˜∫Àµƒ¥¥–¬–‘π¶ƒÐ, ‘⁄±£≥÷“ªº∂ª∫¥Ê¥Û»ð¡øµƒ«∞÷œ¬, µœ÷¡À∂‘Ωœ–°“≥µƒ∏þ–ß”≤º˛÷ß≥÷°£SCache ÷–ªπŒ™ π”√‘≠◊”≤Ÿ◊˜÷∏¡Ó (¿˝»Á, LL/SC ÷∏¡Ó) Ω¯––∂ý∫ÀµƒÕ¨≤Ωº”»Î¡ÀÃÿ ‚…˺∆: µ±“ª∏ˆ ¥¶¿Ì∆˜∫À π”√‘≠◊”≤Ÿ◊˜÷∏¡ÓªÒµ√“ª∏ˆª∫¥Ê–– ±, SCache ‘⁄∂à ±º‰ƒ⁄Ω´Ω˚÷π∞—’‚∏ˆª∫¥Ê––◊™»√∏¯∆‰À˚¥¶¿Ì∆˜∫À°£∏√ ±º‰º‰∏ÙŒ™Àʪ˙ ˝, Àʪ˙µƒ∑∂Œßø…“‘Õ®π˝»Ìº˛Ω¯––≈‰÷√°£Õ®π˝…œ ˆ…˺∆, ∂ý∏ˆ¥¶¿Ì∆˜∫ÀÕ¨ ±’˘«¿Õ¨“ª∏ˆƒ⁄¥Êµÿ÷∑ ±, ø…“‘‘⁄ ±º‰…œ¥Æ––ø™¿¥, ºı…Ÿ¡Àæ∫’˘°£’‚∏ˆÃÿ ‚…˺∆ø…“‘÷∏þ∂ý∫ÀÕ¨≤Ωµƒ–‘ƒÐ, ≤¢ø…“‘∑¿÷π“Ú√ø∏ˆ¥¶¿Ì∆˜∫À∂º’º”– ±º‰π˝∂㨌Þ∑®–Þ∏ƒπ≤œÌ ˝æð∂¯µº÷¬µƒªÓÀ¯œ÷œÛ°£‘⁄ SCache ÷–≤È—Ø ß–ßµƒ«Î«Ûª·œÚœ¬“ªº∂¥Ê¥¢…˱∏∑¢≥ˆ∑√¥Ê«Î«Û°£œ¬“ªº∂¥Ê¥¢…˱∏∞¸¿®ƒ⁄¥Ê, PCI, SPI ªÚ∆‰À˚Õ‚≤ø…˱∏°£ ‘⁄“ªº∂ ˝æðª∫¥Ê√¸÷–µƒº”‘ÿ÷∏¡Ó—”≥ŸŒ™ 4 ∏ˆ ±÷”÷Ð∆⁄£ª‘⁄ Victim Cache √¸÷–, ‘Úª·∏¯’‚Ãı∑√¥Ê÷∏¡Ó¥¯¿¥∂ÓÕ‚ 18 ∏ˆ ±÷”÷Ð∆⁄µƒ—”≥Ÿ£ª»Áπ˚ « Victim Cache “≤ ß–ßµ´ «‘⁄ SCache ÷–√¸÷–µƒ∑√¥Ê÷∏¡Ó, œý±»“ªº∂ª∫¥Ê√¸÷–µƒ«Èøˆ“™∂ý 50 ∏ˆ ±÷”÷Ð∆⁄µƒ—”≥Ÿ, ∆‰÷–∑√Œ SCache –Ë“™µƒ ±º‰Œ™ 11 ∏ˆ ±÷”÷Ð∆⁄, ∆‰À˚—”≥Ÿ∞¸¿®«Î«Û‘⁄∆¨ƒ⁄¥´µðµƒ—”≥Ÿ, “‘º∞Œ™÷ß≥÷¥¶¿Ì∆˜∫ÀΩµ∆µ…˺∆À˘–Ë“™µƒ“Ï≤Ω∂”¡–À˘¥¯¿¥µƒ—”≥Ÿ°£ 6 Loongson 3A3000 ¡˙–æ 3A3000/3B3000÷˜∆µ 1.2Hz®C1.5GHz£¨Œ™4∫À¥¶¿Ì∆˜£¨≤…”√4∏ˆÀƒ∑¢…‰¬“–Ú÷¥––µƒ64 Œª≥¨±Í¡ø¥¶¿Ì∆˜∫ÀGS464E£¨÷ß≥÷ MIPS64 ÷∏¡ÓºØ£¨÷ß≥÷¡˙–æ¿©’π÷∏¡ÓºØ£¨≤…”√12 º∂≥¨±Í¡ø¡˜ÀÆœþ; √ø∫À”–2 ∏ˆ∂®µ„µ•‘™°¢2 ∏ˆ∏°µ„µ•‘™∫Õ 2 ∏ˆ∑√¥Êµ•‘™°£√ø∏ˆ¥¶¿Ì∆˜∫À∞¸∫¨ 64KB ÀΩ”–“ªº∂÷∏¡Óª∫¥Ê∫Õ 64KB ÀΩ”–“ªº∂ ˝æðª∫¥Ê;√ø∏ˆ¥¶¿Ì∆˜∞¸∫¨ 256KB ÀΩ”–∂˛º∂ª∫¥Ê;À˘”–¥¶¿Ì∆˜∫Àπ≤œÌ 8MB »˝º∂ª∫¥Ê°£ ∫Õ¡˙–æ3A2000œý±»£¨≥˝¡À¡˜∆¨π§“’¥”÷––æπ˙º µƒ40ƒ…√◊÷…˝µΩ“‚∑®∞εºÃµƒ28ƒ…√◊CMOS 𧓒£¨¥¶¿Ì∆˜µƒ»˝º∂ª∫¥Ê“≤¥”4MB÷∏þµΩ8MB°£∑Â÷µ∏°µ„–‘ƒÐ24GFlops£¨µ‰–Õπ¶∫ƒ <40W@1.5GHz°£ºØ≥…µƒΩ”ø⁄”–¡Ω∏ˆHT3.0Ω”ø⁄£¨PCIøÿ÷∆∆˜°¢LPC°¢SPI°¢UART°¢GPIO£¨¡Ω∏ˆ72ŒªDDR2/3-1600£¨÷ß≥÷ECC°£ 7 Loongson 3A4000 ¡˙–æ3A4000≤…”√¡˙–æ◊Ó–¬—–∑¢µƒGS464V£¨æ°πС˙–æ3A4000»‘»ª≤…”√28nm𧓒, µ´÷˜∆µÃ·∏þµΩ2.0GHz, ◊€∫œ–‘ƒÐ «…œ“ª¥˙¡˙–æ3A3000µƒ¡Ω±∂°£”√”⁄∆¨º‰ª•¡¨º∞¡¨Ω”«≈∆¨µƒHTøÿ÷∆∆˜¥¯øÌ÷∏þ“ª±∂“‘…œ£¨ƒ⁄¥Êøÿ÷∆∆˜¥”DDR3…˝º∂µΩDDR4£¨∂‘–ȃ‚ª˙÷ß≥÷∏¸º”ÕÍ…∆£¨–߬ ¥ÔµΩ95%“‘…œ°£¡˙–æ3A4000/3B4000“≤ « ◊¥Œ‘⁄∆¨ƒ⁄ºØ≥…¬©∂¥∑¿∑∂…˺∆°¢”≤º˛π˙√ÐÀ„∑®°¢∞≤»´ø…–≈ƒ£øÈ”Î∞≤»´∑√Œ øÿ÷∆ª˙÷∆µƒ¥¶¿Ì∆˜°£¡˙–æ3B4000‘⁄¡˙–æ3A4000µƒª˘¥°…œ÷ß≥÷∂ý¬∑ª•¡¨°£ |

|

|

8 Loongson 3A5000 ¡˙–æ3A5000≤…”√∫Õ¡˙–æ3A4000µƒ¥¶¿Ì∆˜Õ¨—˘µƒGS464EV, ≤…”√12nm𧓒¡˜∆¨, ÷˜∆µÃ·…˝µΩ2.5GHz°£¡˙–æ3A5000“¿»ª «4∫À¥¶¿Ì∆˜£¨∂¯¡˙–æ3C5000Ω´ «“ªøÓ16∫À¥¶¿Ì∆˜°£¡˙–æ3A5000/3B5000 «√ÊœÚ∏ˆ»Àº∆À„ª˙°¢∑˛ŒÒ∆˜µ»–≈œ¢ªØ¡Ï”ÚµƒÕ®”√¥¶¿Ì∆˜£¨ª˘”⁄¡˙–æ◊‘÷˜÷∏¡ÓœµÕ≥LoongArchµƒLA464Œ¢Ω·ππµƒÀƒ∫À¥¶¿Ì∆˜£¨‘⁄”Ρ˙–æ3A4000¥¶¿Ì∆˜±£≥÷“˝Ω≈ºÊ»ðµƒª˘¥°…œ£¨∆µ¬ ÷…˝÷¡2.5GHz£¨π¶∫ƒΩµµÕ30%“‘…œ£¨–‘ƒÐ÷…˝50%“‘…œ°£¡˙–æ3B5000‘⁄¡˙–æ3A5000µƒª˘¥°…œ‘⁄HT0Ω”ø⁄…œ÷ß≥÷“ª÷¬–‘ª•¡™“‘±„÷ß≥÷∂ý¬∑ª•¡¨°£œ¬Õº’π æ¡À∆‰–æ∆¨ºÐππ£∫ |

|

|

µ⁄“ªº∂ª•¡™≤…”√5x5µƒΩª≤Êø™πÿ£¨”√”⁄4∏ˆ¥¶¿Ì∆˜∫À£¨4∏ˆπ≤œÌª∫¥Êƒ£øÈ∫Õ“ª∏ˆIO∂Àø⁄µƒ¡¨Ω”°£µ⁄∂˛º∂ª•¡™≤…”√5x3µƒΩª≤Êø™πÿ£¨¡¨Ω”4∏ˆπ≤œÌµƒª∫¥Êƒ£øÈ£¨¡Ω∏ˆƒ⁄¥Êøÿ÷∆∆˜∫Õ“ª∏ˆIO∂Àø⁄°£IOª∑◊Ðœþ“ªπ≤8∏ˆ∂Àø⁄£¨∑÷±¡¨Ω”4∏ˆHTøÿ÷∆∆˜£¨¬˝ÀŸ ‰»Î ‰≥ˆƒ£øÈ£¨∞≤»´ƒ£øÈ“‘º∞¡Ωº∂Ωª≤Êø™πÿ°£¡Ω∏ˆHTøÿ÷∆∆˜π≤”√16ÃıHT◊Ðœþ£¨ø…“‘◊˜Œ™¡Ω∏ˆ8ŒªHTªÚ“ª∏ˆ16ŒªHT π”√°£ …œ ˆª•¡™Ω·ππ∂º≤…”√∂¡–¥∑÷¿Îµƒ ˝æðÕ®µ¿£¨ŒªøÌ128±»Ãÿ£¨”Î¥¶¿Ì∆˜Õ¨∆µ£ª¥¶¿Ì∆˜∫À∫Õµ⁄“ªº∂Ωª≤Êø™πÿ∂¡Õ®µ¿ «256±»Ãÿ°£ œ¬Õº’π æ¡À¡˙–æ3A5000µƒŒÔ¿ÌπʪÆ∞ÊÕº£∫ |

|

|

8.1 LA464¥¶¿Ì∆˜∫À LA464 «“ª∏ˆ4∑¢…‰µƒ≥¨±Í¡ø¥¶¿Ì∆˜£¨”–4∏ˆ∂®µ„µ•‘™£¨2∏ˆ256ŒªµƒœÚ¡øµ•‘™∫Õ2∏ˆ∑√¥Êµ•‘™°£√ø∏ˆœÚ¡øµ•‘™÷ß≥÷8∏ˆµ•æ´∂»ªÚ4∏ˆÀ´æ´∂»≥Àº”‘ÀÀ„£ª∑√¥Êµ•‘™÷ß≥÷256Œª¥Ê¥¢∑√Œ .œ¬Õº’π æ¡ÀLA464¥¶¿Ì∆˜∫ÀµƒŒ¢ºÐππ£∫ |

|

|

8.1.1 π≤œÌª∫¥Ê Scacheƒ£øÈ «¡˙–æ3A5000ƒ⁄≤øÀ˘”–¥¶¿Ì∆˜∫Àπ≤œÌµƒL3ª∫¥Ê£¨≤…”√16¬∑◊Èœý¡™£¨”…ª∫¥Êπп̃£øÈ∫Õª∫¥Ê∑√Œ ƒ£øÈ◊È≥…£∫ ª∫¥Êπп̃£øÈ ∏∫‘¥¶¿Ì¿¥◊‘¥¶¿Ì∆˜∫ÕDMAµƒ∑√Œ «Î«Û ª∫¥Ê∑√Œ ƒ£øÈ ∏∫‘¥Ê∑≈ª∫¥Ê±Í«©£¨ƒø¬º∫Õ ˝æð 8.1.2 SMPª•¡™ Õ®π˝HTΩ¯––ª•¡™ø…“‘◊È≥…2¬∑£¨4¬∑£¨8¬∑ªÚ16¬∑SMPœµÕ≥£¨’˚∏ˆœµÕ≥ŒÔ¿Ìµÿ÷∑øÌ∂»Œ™48Œª£¨µÿ÷∑∏þ4Œª”√¿¥ ∂±µ•∏ˆΩ⁄µ„£¨√ø∏ˆΩ⁄µ„ µº ø…”√µÿ÷∑ø’º‰ «44Œª°£µ±œµÕ≥Ω⁄µ„ ˝ƒø≤ª◊„16 ±£¨–Ë“™≈‰÷√¬∑”……Ë÷√ºƒ¥Ê∆˜£¨±£÷§√ª”–∂‘”¶Ω⁄µ„µƒµÿ÷∑ƒÐπª∑µªÿœÏ”¶°£ 9 Loongson 3A6000 ¡˙–æ3A6000¥¶¿Ì∆˜ «¡˙–æµ⁄Àƒ¥˙Œ¢ºÐπ𵃠◊øÓ≤˙∆∑£¨ºØ≥…4∏ˆ◊Ó–¬—–∑¢µƒ∏þ–‘ƒÐ6∑¢…‰64ŒªLA664¥¶¿Ì∆˜∫À°£÷˜∆µ¥ÔµΩ2.5GHz£¨÷ß≥÷128ŒªœÚ¡ø¥¶¿Ì¿©’π÷∏¡Ó£®LSX£©∫Õ256Œª∏þº∂œÚ¡ø¥¶¿Ì¿©’π÷∏¡Ó£®LASX£©£¨÷ß≥÷Õ¨ ±∂ýœþ≥úº ı£®SMT2£©£¨»´–æ∆¨π≤8∏ˆ¬þº≠∫À°£¡˙–æ3A6000∆¨ƒ⁄ºØ≥…À´Õ®µ¿DDR4-3200øÿ÷∆∆˜£¨ºØ≥…∞≤»´ø…–≈ƒ£øÈ£¨ø…÷π©∞≤»´∆Ù∂Ø∑Ω∞∏∫Õπ˙√У®SM2°¢SM3°¢SM4µ»£©”¶”√÷ß≥÷°£∫Õ3A5000œý±»£¨÷˜“™ «∏¸–¬¡À¥¶¿Ì∆˜ƒ⁄∫À£¨–æ∆¨’˚úÐππ»Áœ¬ÕºÀ˘ æ£∫ |

|

|

µ⁄“ªº∂ª•¡¨≤…”√ 5x5 µƒΩª≤Êø™πÿ£¨”√”⁄¡¨Ω”Àƒ∏ˆ¥¶¿Ì∆˜∫À°¢Àƒ∏ˆπ≤œÌ Cache ƒ£øÈ°¢“‘º∞“ª∏ˆ IO ∂Àø⁄¡¨Ω” IO-RING°£ µ⁄∂˛º∂ª•¡¨≤…”√ 5x3 µƒΩª≤Êø™πÿ£¨¡¨Ω” 4 ∏ˆπ≤œÌ Cache ƒ£øÈ£¨¡Ω∏ˆ DDR4 ƒ⁄¥Êøÿ÷∆∆˜°¢ “‘º∞“ª∏ˆ IO ∂Àø⁄¡¨Ω” IO-RING°£ IO-RING ∞¸∫¨∂ý∏ˆ∂Àø⁄£¨¡¨Ω”∞¸¿® HT øÿ÷∆∆˜£¨MISC ƒ£øÈ£¨SE ƒ£øÈ”Î¡Ωº∂Ωª≤Êø™πÿ°£HT øÿ÷∆∆˜ƒ⁄ºØ≥…“ª∏ˆ DMA øÿ÷∆∆˜£¨DMA øÿ÷∆∆˜∏∫‘ IO µƒ DMA øÿ÷∆≤¢∏∫‘∆¨º‰“ª÷¬–‘µƒŒ¨ª§°£ …œ ˆª•¡¨Ω·ππ∂º≤…”√∂¡–¥∑÷¿Îµƒ ˝æðÕ®µ¿£¨ ˝æðÕ®µ¿øÌ∂»Œ™ 128 Œª£¨π§◊˜‘⁄”Î¥¶¿Ì∆˜ ∫ÀœýÕ¨µƒ∆µ¬ £¨”√“‘÷π©∏þÀŸµƒ∆¨…œ ˝æ𥴠‰°£¥ÀÕ‚£¨“ªº∂Ωª≤Êø™πÿ¡¨Ω” 4 ∏ˆ¥¶¿Ì∆˜∫À”Î scache µƒ∂¡ ˝æðÕ®µ¿Œ™ 256 Œª£¨“‘÷∏þ∆¨ƒ⁄¥¶¿Ì∆˜∫À∑√Œ scache µƒ∂¡¥¯øÌ°£ SCache ƒ£øÈ «¡˙–æ 3A6000 ¥¶¿Ì∆˜ƒ⁄≤øÀ˘”–¥¶¿Ì∆˜∫ÀÀ˘π≤œÌµƒ»˝º∂ª∫¥Ê°£SCache ƒ£øÈ÷ß≥÷16 œÓª∫¥Ê∑√Œ ∂”¡–£¨≤…”√ 16 ¬∑◊Èœý¡™Ω·ππ£¨÷ß≥÷ ECC –£—È°£ π≤ œÌª∫¥Êƒ£ øÈ∞¸¿®π≤œÌ ª∫¥Êπп̃£øÈscachemanage º∞π≤œÌª∫¥Ê∑√Œ ƒ£øÈscacheaccess°£Scachemanage ƒ£øÈ∏∫‘¥¶¿Ì∆˜¿¥◊‘¥¶¿Ì∆˜∫Õ DMA µƒ∑√Œ «Î«Û£¨∂¯π≤œÌª∫¥Êµƒ±Í«©°¢ƒø¬º∫Õ ˝æðµ»–≈œ¢¥Ê∑≈‘⁄ scacheaccess ƒ£øÈ÷–°£Œ™ΩµµÕπ¶∫ƒ£¨π≤œÌª∫¥Êµƒ±Í«©°¢ ƒø¬º∫Õ ˝æðø…“‘∑÷ø™∑√Œ £¨π≤œÌ ª∫¥Ê◊¥Ã¨Œª°¢w Œª”αͫ©“ª∆¥Ê¥¢£¨±Í«©¥Ê∑≈‘⁄ TAG RAM ÷–£¨ƒø¬º¥Ê∑≈‘⁄ DIR RAM ÷–£¨ ˝æð¥Ê∑≈‘⁄ DATA RAM ÷–°£ ߖ߫ΫÛ∑√Œ π≤œÌª∫¥Ê£¨Õ¨ ±∂¡≥ˆÀ˘”–¬∑µƒ±Í«©°¢ƒø¬º£¨≤¢∏˘æð ±Í«©¿¥—°≥ˆƒø¬º£¨≤¢∏˘æð√¸÷–«Èøˆ∂¡»° ˝æð°£Ãʪª«Î«Û°¢÷ÿ ÃӫΫÛ∫Õ–¥ªÿ«Î«Û÷ª≤Ÿ◊˜“ª¬∑µƒ ±Í«©°¢ƒø¬º∫Õ ˝æð°£ LA664 «¡˘∑¢…‰ 64 Œªµƒ¥¶¿Ì∆˜∫À°£‘⁄¡˙–æ 3A6000 ÷–µƒ∂ý∏ˆ LA664 ∫À“‘º∞π≤œÌª∫¥Êƒ£øÈÕ®π˝ AXI ª•¡¨Õ¯¬Á–Œ≥…“ª∏ˆ∑÷≤º Ωπ≤œÌ∆¨…œƒ©º∂ª∫¥Êµƒ∂ý∫ÀΩ·ππ°£LA664 ÷ß≥÷Õ¨ ±∂ýœþ≥úº ı(SMT2)£ª”–Àƒ∏ˆ∂®µ„°¢Àƒ∏ˆœÚ¡ø°¢Àƒ∏ˆ∑√¥Êµ•‘™£ª√ø∏ˆœÚ¡øµ•‘™øÌ∂»Œ™ 256 Œª£¨◊Ó∂ý÷ß≥÷ 8 ∏ˆµ•æ´∂»ªÚ 4 ∏ˆÀ´æ´∂»≥Àº”‘ÀÀ„£ª ∑√¥Êµ•‘™÷ß≥÷ 256 Œª¥Ê¥¢∑√Œ £¨–ȵÿ÷∑Œ™ 64 Œª£¨ŒÔ¿Ìµÿ÷∑Œ™ 48 Œª£ª“ªº∂÷∏¡Óª∫¥Ê∫Õ ˝æðª∫¥Ê¥Û–°∏˜Œ™ 64KB£¨4 ¬∑◊Èœý¡™£ª Victim Cache ◊˜Œ™ÀΩ”–∂˛º∂ª∫¥Ê£¨¥Û–°Œ™ 256KB£¨16 ¬∑◊Èœý¡¨£ª “ªº∂ª∫¥Ê µœ÷∆Ê≈º–£—È£¨∂˛º∂°¢∆¨…œƒ©º∂ª∫¥Ê µœ÷ ECC –£—È£¨æ˘÷ß≥÷“ªŒªæ¿’˝°£ ≤ŒøºŒƒœ◊LoongArch-Vol1-v1.02Loongson 3A5000/3B5000 Processor Reference Manual - Multicore Processor Architecture, Register Descriptions and System Software Programming Guide, n.d.Wang H., Wang W., Wu R., Hu W., 2015. ¡˙–æGS464E¥¶¿Ì∆˜∫ÀºÐππ…˺∆. Sci. Sin.-Inf. 45, 480®C500. https://doi.org/10.1360/N112014-00292Hu, W., Wang, J., Gao, X., Chen, Y., Liu, Q., Li, G., 2009. Godson-3: A Scalable Multicore RISC Processor with x86 Emulation. IEEE Micro 29, 17®C29. https://doi.org/10.1109/MM.2009.30W. Hu et al., "Godson-3B1500: A 32nm 1.35GHz 40W 172.8GFLOPS 8-core processor," 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 2013, pp. 54-55, doi: 10.1109/ISSCC.2013.6487634.W. Hu et al., "Godson-3B: A 1GHz 40W 8-core 128GFLOPS processor in 65nm CMOS," 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2011, pp. 76-78, doi: 10.1109/ISSCC.2011.5746226.Gao, X., Chen, Y.-J., Wang, H.-D., Tang, D., Hu, W.-W., 2010. System Architecture of Godson-3 Multi-Core Processors. J. Comput. Sci. Technol. 25, 181®C191. https://doi.org/10.1007/s11390-010-9315-3Hu W W, Tang Z M. Microarchitecture design of the Godson1 Processor. Chinese Journal of Computers, April 2003, 26(4): 385-396.Hu W W, Zhang F X, Li Z S. Microarchitecture of the Godson-2 processor. Journal of Computer Science and Technology, March 2005, 20(2): 243-249.Loongson 3A6000 Processor Reference Manual - Multicore Processor Architecture, Register Descriptions and System Software Programming Guide, n.d. |

|

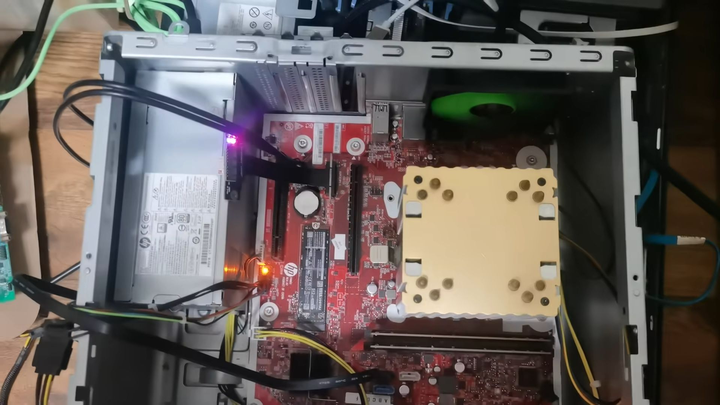

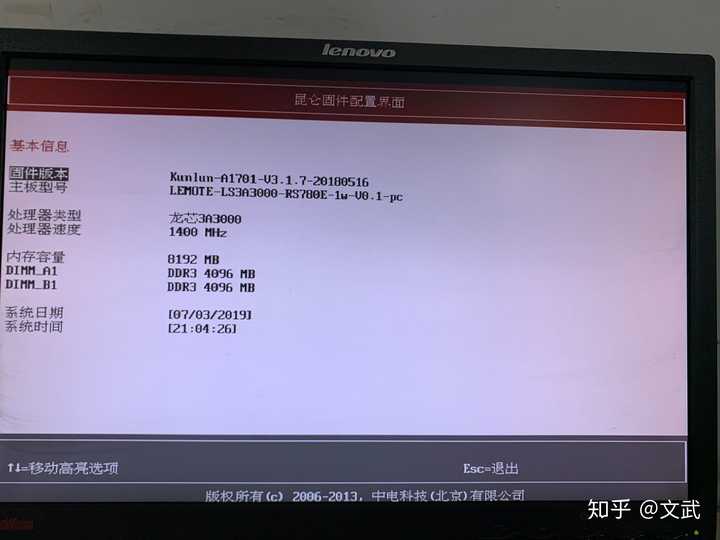

ø¥±®µ¿√ª”√£¨’˝∫√ΩÒƒÍ6‘¬ªπ≤Œº”“ª∏ˆœýπÿ±»»¸£¨æÕ «ª˘”⁄¡˙–æø™∑¢£¨‘Ÿ∂ý–≈œ¢≤ª±„Õ∏¬∂°£ Œ“√«ƒ√µΩµƒª˙∆˜ «∫≈≥∆◊Ó–¬ºº ıµƒ¡˙–æ3a3000 4∫À–ƒ£¨¥Ó≈‰8gƒ⁄¥Ê£¨500gπÃè°≠ |

|

|

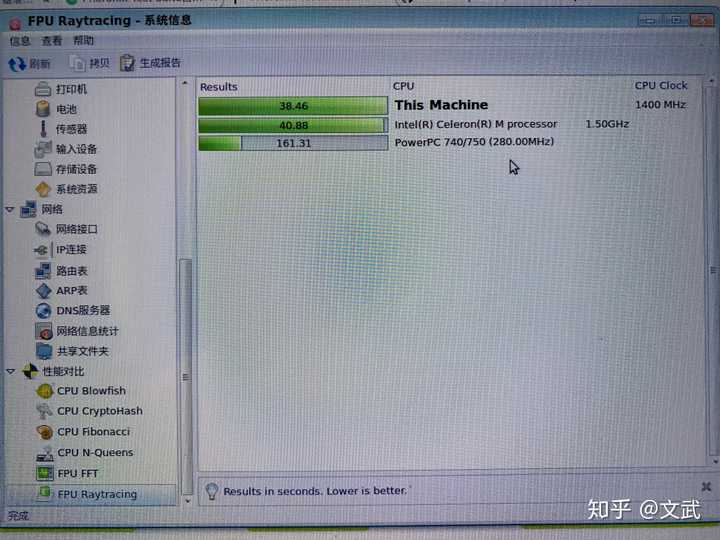

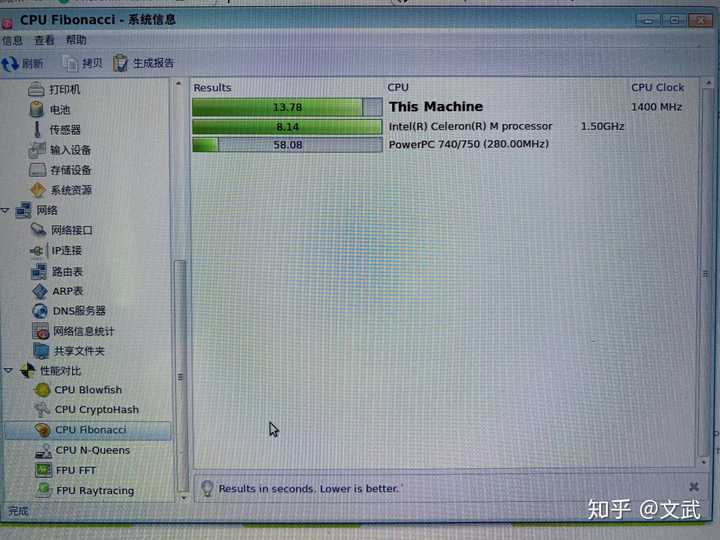

bios¿Ô√Êø¥µΩ «’‚—˘µƒ°≠ ÀµÀµŒ“√« π”√ƒ¨»œœµÕ≥µƒÃ—Ȱ£ƒ¨»œœµÕ≥ «÷–±Í˜Ë˜Î◊¿√Ê∞Ê£¨∫Û√Ê”…”⁄docker–Ë“™ƒ⁄∫À“ª∏ˆπÿ”⁄ƒ⁄¥Êµƒµ˜∂»÷ß≥÷ªª≥…∑˛ŒÒ∆˜∞ʱ氣∂‘”⁄œµÕ≥uiΩªª•µ»≤ª∂ý◊ˆ∆¿º€°£ ΩˆΩˆ∂‘”⁄–‘ƒÐ£¨æþ×π≤‚Œ“√«√ª≤‚º´œÞ£¨‘⁄jvm≈ÐŒ“√«œÓƒø£¨µ±»ªªπŒ¥æ≠◊®√≈”≈ªØ ±£¨guiæÕª·≤˙…˙»‚—€ø…º˚µƒø®∂Ÿ°£Õ¨ ±cpu’º”√º∏∫ıÏ≠¬˙°£ µ±»ªŒ““≤◊ˆ¡À◊®√≈µƒ–‘ƒÐ≤‚ ‘£¨◊‘¥¯µƒ–‘ƒÐ≤‚ ‘Ω·π˚œ‘ 棨≈Ðfpu”ÎÏ≥≤®ƒ«∆ıª˘±æ”λ¸—Ôm“ª÷¬°≠ |

|

|

|

|

|

À˘“‘æÕ’‚∏ˆ–‘ƒÐ∏˘±æ√ª∞Ï∑®¬˙◊„ƒø«∞∂ý ˝µƒ–Ë«Û£¨ø…ƒÐƒÐ¬˙◊„µƒ“≤æÕ «ª˘¥°µƒŒƒ◊÷¥¶¿Ì ¬ŒÒÃ·Ωªµ»°≠ µ´…‘Œ¢÷ÿ“ªµ„µƒ–Ë«ÛæՌރЌ™¡¶£¨’‚æÕª·√Ê¡Ÿœ˚∑—’þ≤ª¬Úµ•µƒ«Èøˆ°≠±œæπƒ„≤ªª·œ£Õ˚◊‘º∫‘⁄9012ƒÍ¬ÚµƒµÁƒ‘∏…10ƒÍ«∞µÁƒ‘∏…µƒªÓ°≠ ∏¸∫Œøˆªπ”–œµÕ≥≤Óæý‘⁄°£ π˙≤˙ªØ£¨»Œ÷ÿ∂¯µ¿‘∂°£µ´◊˜Œ™“ª∏ˆ∫œ∏Òµƒø™∑¢’þ”¿‘∂≤ªœ£Õ˚”√ªßŒ™°∞∞Æπ˙°±¬Úµ•°£ |

|

|

| [ ’≤ÿ±æŒƒ] °æœ¬‘ÿ±æŒƒ°ø |

| ˝¬Î ◊Ó–¬Œƒ’¬ |

| ª™Œ™◊‘º∫—–∑¢µƒ–æ∆¨Œ™ ≤√¥»¥‘Ω¬Ù‘ΩπÛ¡À£ø |

| Beats ‘⁄±ª∆ªπ˚ ’π∫∫Û£¨∆‰°∏≥±≈∆°π Ù–‘ «∑Ò |

| –°√◊∑€ÀøŒ™ ≤√¥¥Û∂º «ƒÍ«·»À£øƒÍ¡‰¥Û¡À÷Æ∫Û |

| ∆ÿ 3 ‘¬π˙ƒ⁄ –≥° ÷ª˙≥ˆªı¡ø 2115 ÕÚ≤ø£¨Õ¨±» |

| Œ™ ≤√¥’≈—©“™º±¥“¥“∞—◊‘º∫∫Õ◊‘º∫µƒª˙≥µ∆∑≈∆ |

| »Á∫Œ∆¿º€MacBook Neo£ø |

| Œ™ ≤√¥ ÷ª˙”–BLÀ¯£¨∂¯µÁƒ‘√ª”–ƒÿ£ø |

| –°√◊14UltraÀ—–«ÀŸ∂»±»ª™Œ™Mate60proªπøÏ£¨ |

| »Á∫Œø¥¥˝ 3999 ‘™∆ €µƒ OPPO Find X7 œµ¡– |

| ª™Œ™ ÷ª˙»˝Ãϱÿ–Î ‰“ª¥Œ√ЬΠ«≤ª «ƒ‘≤–…˺∆ |

| …œ“ª∆™Œƒ’¬ œ¬“ª∆™Œƒ’¬ ≤Èø¥À˘”–Œƒ’¬ |

|

|

|

|

”È¿÷…˙ªÓ:

µÁ”∞∆±∑ø

”È¿÷»¶

”È¿÷

»ı÷«

ª—–

÷–ª™≥« –

”°∂»

œ…º“

¡˘ÿ≥

∑√≈

∑ÁÀÆ

π≈«Æ±“Ωª¡˜◊®”√

µˆ”„

À´…´«Ú

∫Ωø’ƒ∏Ω¢

Õ¯«Ú

∆π≈“«Ú

÷–π˙≈Æ≈≈

◊„«Ú

nba

÷–≥¨

≈Ð≤Ω

œÛ∆Â

ÃÂ≤Ÿ

Ω‰…´

…œ∫£ƒ–ø∆

80∫Û

◊„«Ú: ¬¸≥« ¿˚ŒÔ∆÷∂” Õ–Ãÿƒ…ƒ∑»»¥Ã ª º“¬Ìµ¬¿Ô ”»ŒƒÕºÀπ ¬Þ¬Ì ¿≠∆Î∞¬ √◊¿º ¿Ô∞∫ ∞Õ¿Ë •»’∂˚¬¸ ¬¸¡™ |

| Õ¯’æ¡™œµ: qq:121756557 email:121756557@qq.com ÷™ ∂ø‚ |