| |

|

| 知识库 -> 数码 -> 现在ssd都可以用堆叠技术了,为什么CPU不能多堆几层呢,这样性能不就提升了吗? -> 正文阅读 |

|

|

[数码]现在ssd都可以用堆叠技术了,为什么CPU不能多堆几层呢,这样性能不就提升了吗? |

| [收藏本文] 【下载本文】 |

|

现在ssd都可以用堆叠技术了,为什么CPU不能多堆几层呢,反正现在光刻机都14nm了,就算导线层也不必做的那么大,如果能堆叠2层,CPU 的性能不就差… |

|

你就像那冬天里的一把火 熊熊火焰温暖了我的心窝 每次当你悄悄走进我身边 火光照亮了我 |

|

看到这汗流浃背了 前两代的intel火炉,单颗cpu干上300w,360一体水都压不住,die面积只有257平方毫米,功率密度大于1w每平方毫米,往死里超的时候积热现象颇严重,这还是算上核显和缓存平均下来的量 amd的zen4火炉,默认功耗170w,360水一样压不住,核心die面积只有70平方毫米,功率密度同样大于1w每平方毫米。考虑到zen4积热更加爆炸,实际功率密度应该高不少 不说叠多了,叠两层,你散热该怎么办? 温差大了,硅片是真的能炸给你看的 有的评论可能没看懂我在说什么 问题不在于散热功率,在热密度过大,传热困难,俗称积热 两层乃至更多层高功率硅片,下面那层的热量传不出来,你表层散热性能再强也没用,到时表面冰凉内心火热,温差巨大直接干炸核心 |

|

CPU堆核心不用竖着叠,人家横着堆就行了。 |

|

|

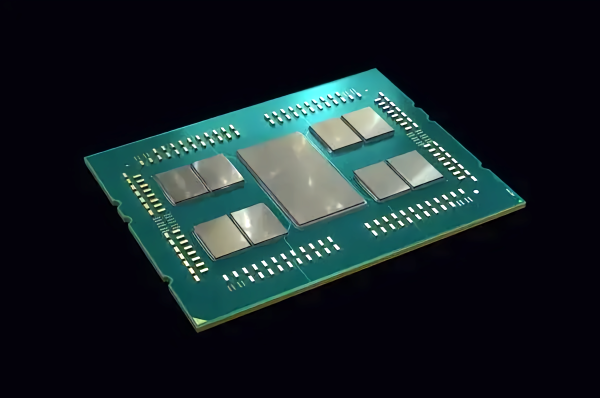

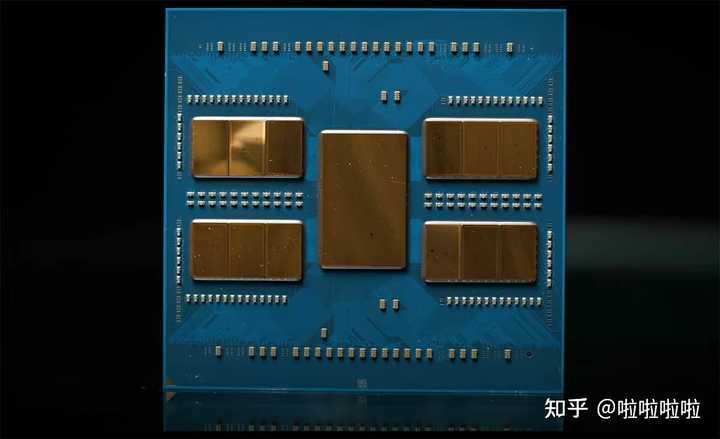

5995wx,总共8个die,相当于八颗5700X合在一起,一共64核心,128个线程。 |

|

SSD搞堆叠,是为了提升存储密度。 SSD里边都是浮动栅,只有擦除、编程时需要通电,加上有主控,能做磨损平衡。 结果就是不会有大量电路同时通电的情况,基本每时每刻都只有一小部分通电了。 所以,即使堆叠,它的热密度也不大。 你要是天天跑分,pcie4和5的固态,它也会过热掉速,也要加散热器。 而CPU,设计就需要考虑全部或近乎全部电路都通电的情况。 毕竟CPU设计就是搞计算的,三秒真男人谁敢用? CPU需要做到持续满负荷运算,在外部散热设施满足条件的情况下,不因为自身热密度问题,造成影响正常性能的积热。 一句话,SSD堆叠能带来正面作用,CPU不能。 自然,堆叠也不是你想得那么简单,SSD可以不良的部分标记为坏块,然后屏蔽掉,反正都是存储单元,都一样。 CPU则不行,很多电路不能互相替代,需要故意加冗余才能保证良品率,这可是要增加成本浪费面积的,堆叠的话,良品率可能就撑不住了。 |

|

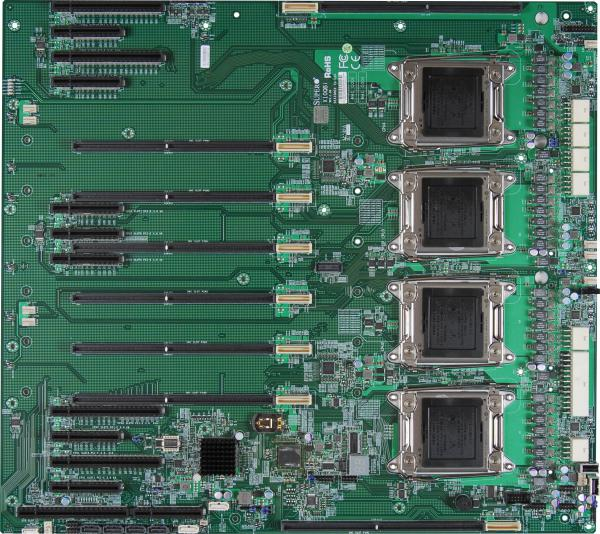

你猜这种主板用来干嘛? |

|

|

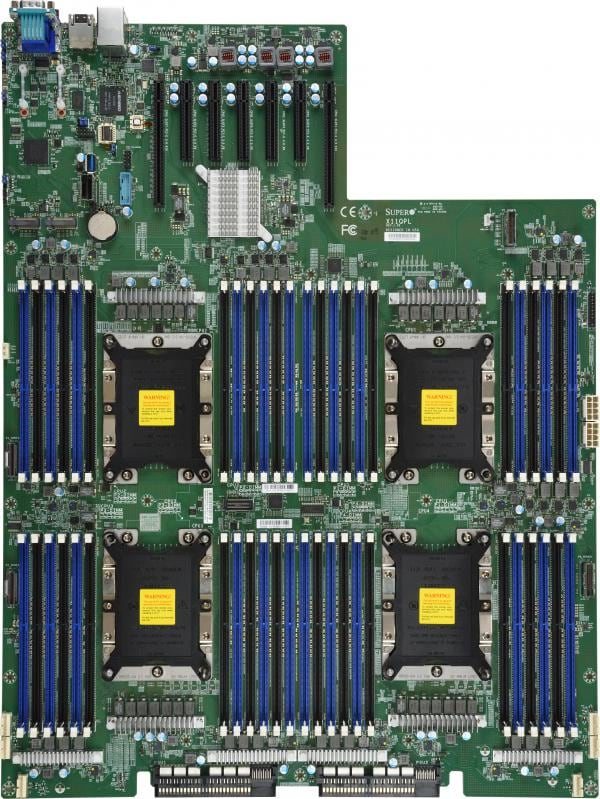

或者这种? |

|

|

至少良品率更高,成本更低 |

|

不知道题主有没有吃过整一大块的炖牛肉和超薄的牛肉片啊。 牛肉片我拿滚烫的火锅里涮个10秒钟可以吃了。 一整大块牛肉你放进火锅里涮个30分钟都炖不烂。 哪怕不是整块的肉,就是厚一倍的牛肉片吧,你涮10秒能吃吗?还是没熟透。 因为你的火锅就100℃,热量传递速度就这么快,牛肉变厚了,那么同样要把最中间的肉加热熟,就需要更长的时间。 同样的,你处理器的散热器散热效率就那么高,你把芯片做厚一倍,芯片外层的热量还没被散热器带走呢,里面的热量还在堆积,超过芯片承受能力,直接里面就积热报废了。 除非你能把芯片材料的热传递效率提升一倍,超快速的把核心热量传导到外部。 但是芯片材料的热传递,在不影响其他性能指标的前提下,哪有那么快提升,材料学的进步慢的要死。 |

|

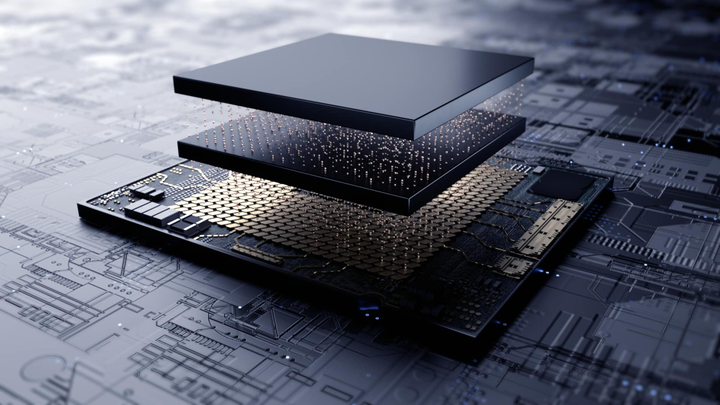

你以为的多堆几层 |

|

|

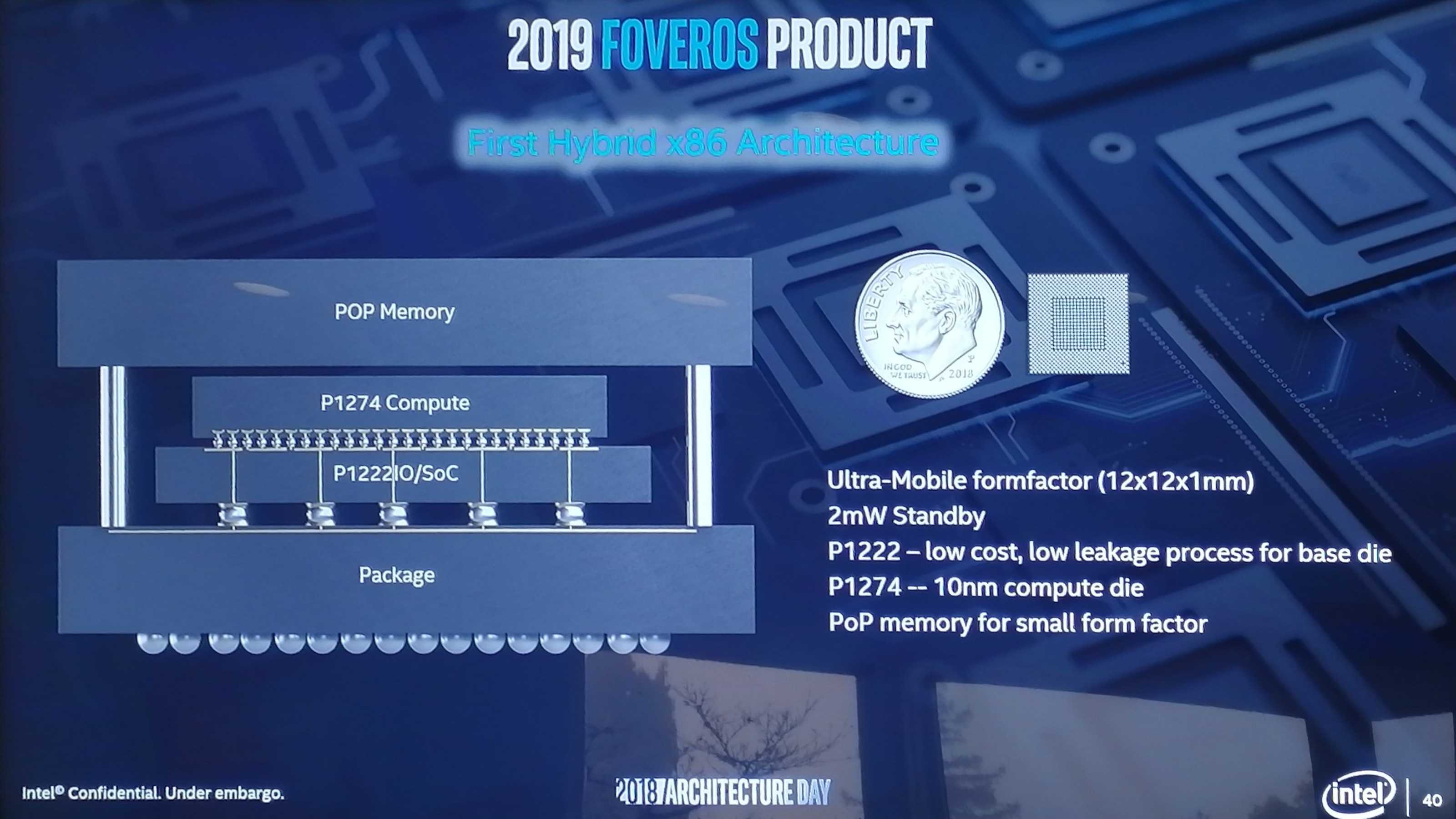

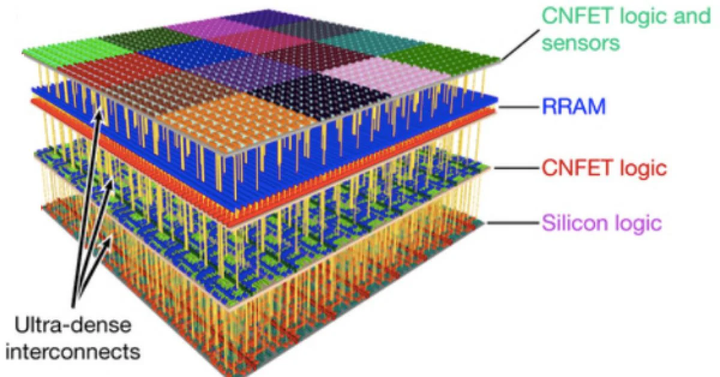

intel Foveros,仅适用于低功耗芯片 实际上的“多堆几层” |

|

|

服务器领域广泛使用的“多CPU体积压缩技术” 你就说集成度高不高吧( |

|

其实是有的。 现在的AMD CPU就是几片小的堆叠在一片大的上面。 只不过那片大的并没有计算的能力,某种意义上只是一块很小的“主板”。 2017年我在日本参加某行业技术会议的时候,英特尔的一名研发人员(阿三哥,好像很有名的样子)也做过相关的演讲,研究了CPU的多层堆叠。 但是结果并不理想。具体细节我也忘记得差不多了,总的来说就是难度很高且(从费用对效果角度来说)没有什么意思。 最终研究方向转向和AMD类似的,将不同功能的芯片(比如CPU和GPU)堆叠在下面一块更大的芯片上。好处主要是下面那块芯片可以采用更为粗糙一些的工艺(因为集成度要求更低),降低总体成本。 还有一个好处就是可以更加方便的实现芯片的定制化。为不同的顾客定制芯片,只需要在下面那块芯片上堆上不同的上层芯片。 RAM以及SSD能多层垂直堆叠的最主要原因还是密度低且电路高度重复。而且工作主频也低,所以发热相对小。 |

|

其实cpu就是这么干的,不过不是立体堆叠,下图为我司Bergamo型号CPU芯片,左右共计12颗CCD(每个CCD有8个core)共计96核心,这种多芯片堆叠的好处在于提高光刻的良率降低生产成本。相较于立体堆叠,平面堆叠的优点是利于散热,不需要设计硅通孔进行芯片间的立体通信,设计相对简单;缺点是不同芯粒间互相通信难效率低、难度大(高频信号对信号传输线的长度很敏感)。对于高功率芯片,主要出于散热考量进行平面堆叠,低功率芯片可以进行立体封装/堆叠,例如苹果手机的芯片(散热差也是苹果手机性能差的主要原因)。 |

|

|

|

|

不是抖机灵,华为确实发布过这个技术, 14nm +14nm > 7nm |

|

CPU和GPU这种计算密集的逻辑电路功耗非常高,直接堆叠散热肯定会爆炸。 考虑zen系列这种chiplet的架构,把各种die堆在一起也可以显著降低die的间距,从而减少通信的延迟,提高通信的带宽,能显著改善目前跨die访问延迟高,带宽有限的困境。 为了解决散热问题,势必在堆叠中引入微通道流体散热的结构,最终将热量均匀分散到较大的基板上,再通过传统散热器带走。这种集成的工艺复杂性目前来说也是过高的,但必然是未来的发展方向之一。 |

|

这是一个非常具有前瞻性的问题。事实上,类似的技术,即三维集成电路(3D IC)技术,已经在研发中,并在某些特定应用领域取得了实质性的成功。但是,为什么它尚未在CPU设计中大规模采用呢?其中涉及到几个主要因素:热管理、制程复杂性、临界信号传输速度以及成本。 |

|

|

1. 热管理 当前的CPU在运行过程中会产生大量的热量,需要通过散热设备将热量有效地传导出去。然而,如果采用堆叠技术,由于层间的热阻较大,内层的热量会很难传到外部,可能会导致内部过热,这对CPU的可靠性和寿命都有严重影响。 2. 制程复杂性和成本 在现有的半导体制造技术基础上,尝试对逻辑晶体管进行堆叠,不仅会大大加大制造工艺的复杂度、引入更多可能的失效模式,而且设备和材料的成本也会显著增加。 3. 临界信号传输速度 在多层的集成电路中,从最底层传至最顶层信号的传输时延将比单层结构显著增大,这会对高速逻辑电路的性能造成限制。 |

|

|

尽管如此,为了进一步提高集成度和性能,业界正在积极研究三维集成技术,也取得了一些早期的成功。例如,HBM(High Bandwidth Memory)就是一种成功的堆叠内存技术,它将内存直接堆叠在一起,并通过封装内的超高速互连通道与芯片通信,从而在相同的功耗下实现了比传统内存更高的带宽。 未来,随着新材料、新设备、封装技术和互连技术等的发展,可以预见堆叠技术或许有望在更广泛的领域得到应用,以突破"摩尔定律"的规模化壁垒,实现更高效和绿色的计算。 然而,这肯定是一个漫长的过程,需要科研人员不断地探索和克服难题。就像亚历山大・格拉汉姆・贝尔曾经说过,“当一扇门关闭时,另一扇门打开”。对于科技而言,永恒的主题是突破和创新。 可以预见,更高效、低功耗和高可靠性的技术仍在我们的不远的未来等待着我们去发掘和研究,也让我们对电子科技的未来期待满满。 |

|

其实最主要是,目前cpu发热量已经很大了,核心热量也无法完全排出,再堆叠的话画面太美… 新提出的方案已经都直接将微细水管直接嵌入晶体管用于排出核心热量,但目前这个还是个方案还没实现…… |

|

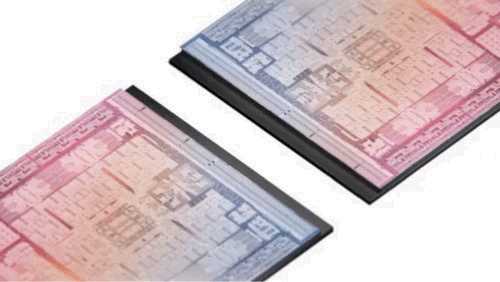

如今动辄几百瓦功耗的CPU,动辄近100度的核心温度,你要把两片叠加在一起,纳米级工艺叠加在一起的芯片,散热怎么处理? 如果你觉得可以,买两颗CPU自己叠不就行了,甚至还可以玩4路8路CPU,操作系统不支持也可以自己每个CPU上单独安装一个系统呗! 其实苹果就给过一个解决方案,但是不是叠加,而是利用UltraFusion技术实现芯片互联,也就是这样。 |

|

|

最后一天,最高9999元红包,最好运! |

|

|

广告 2024京东年货节京享红包 01.17 11:06 - 02.06 00:00 领取京享红包享受更多优惠 去领取? 其实这种问题我估计问的人也大概知道,如果可以叠加,那早就叠了! 其实有比你这个思路更简单的逻辑,想当年CPU还是几十几百MHz的时代,英特尔那帮工程师想的很简单,100MHz的处理器不够快,那就让主频提高到2000MHz,那样速度不就提升20倍了吗?反正最后英特尔做到了。 但是从2000MHz提升到4000MHz、5000MHz,就变得异常困难了! 然后那帮工程师就有了题主一样的睿智,既然一个CPU(一个核心)速度已经不好提升了,那要是搞两个呢?结果真就搞出了双核处理器。再然后呢?如今十几个甚至五六十个核心的CPU都不是什么新鲜事了! |

|

|

你说为什么处理器核心不往100、200核心上堆积呢!因为不划算了!因为良品率太低了! 而英特尔给的解决方案很简单,那就是你真的需要,那就多买几片处理器吧! |

|

|

广告 英特尔(Intel) i9-14900KF 酷睿14代 处理器 24核32线 京东 ¥4349.00 去购买? |

|

cpu功率太大,多堆几层全速运行马上就撞温度墙,然后降频降速,不划算。不如只用一层,做好散热还能保持全速运行。 但是可以在平面上堆叠,单核双核四核八核之类。貌似最早的双核就是硬把两个单核堆在一块 |

|

竖向堆叠会产生严重的积热问题,所以厂商选择横向堆,比如至强铂金系列。 |

|

|

|

|

|

|

|

看了一堆,没有说到点的,真正的限制应该是出在针脚上。 每片CPU底部都有一大堆针脚,这是它与外界进行信息交换的接口,而且为了减少传输时间,就需要大量并行针脚,以实现多通道的同步传输。 因为一条针只能连接一条通道,多通道同步传输就导致CPU需要很多针脚,而且为了保障可安装性,只能把这些针脚都铺在一个平面上,于是就占满了CPU的大部分底面积。 针脚的粗细与间隔都是有严格限制的,因为太细就会电流太大,升温太快,太密集又会互相电磁干扰,所以CPU的最小底面积是有极限值的。 虽然对于CPU内部来说,这些针脚是多通道复用的,但针脚的传输频率是有限的,各计算单元只能在有限时间里占用针脚,所以针脚的数量与芯片内部集成的门数量也是有限制的。 如果对CPU进行堆叠,需要针脚的数量还是不变的,于是底面积基本不会有变化,堆叠没有意义。 如果要突破针脚的限制,那么就得把内存硬盘之类的功能往CPU里搬,这不现实。 |

|

还嫌积热不够多么 |

|

SSD/DRAM都是功能单一的易失性/非易失性存储器,3D堆叠时需要考虑的问题不多。 但是对于CPU而言,除了处理器核内部逻辑外,还需要考虑互联、存储、IO…等多方面的因素,简单的3D堆叠对它们的影响可能很复杂。除此之外,还有一个非常重要的点(也许是更重要的点)那就是散热问题,CPU的动态功耗要远远高于memory,如何实现几百瓦的CPU die 3D堆叠散热是个大问题。 当然,现在还是有利用3D堆叠实现性能提升的算力芯片,不过通常是计算die和存储die之间的堆叠,譬如AMD的3D VCache,比方大算力芯片中多起来的DRAM 3D合封。 |

|

首先,没人单独关心性能,大家关心的都是比性能,比如性价比/能效/密度。 除了积热,还有缺乏需求。 CPU目前不需要小型化,它远远不是系统密度的瓶颈,供电/散热才是。反而巴掌大的Xeon/EPYC还很好看,就是有点太软了 ( ? ?ω?? )? 但其实堆叠是有别的用途的,理论上来说它可以充分利用Z轴把一个时钟域做大,只是我们需求和科技树都还没爬到那。 |

|

内存芯片结构简单、发热量不大, 所以堆叠这种粗活比较合适。 CPU,考虑到发热量,最好还是平铺吧。 |

|

nand什么功耗,cpu什么功耗? |

|

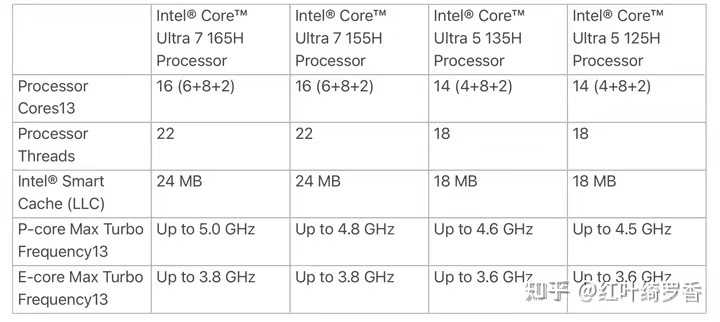

事实上最新的酷睿ultra就是堆叠的,是为了提高不同模块间的通信效率 |

|

AMD的X3D系列了解一下,虽然只是堆叠了一层L3缓存,核心发热就已经失控了。 而消费级逻辑电路本身就更难通过规模横向扩展,如果再搞3D堆叠,工艺难度、设计难度不说,功耗控制带来的瓶颈很容易就抵消横向扩展带来的优势了。 至于企业级应用的横向扩展,人家一个巴掌大的封装,往里面疯狂放DIE就行了,一个封装8个DIE,还不爽直接上4个CPU,怎么也够用了,何必搞3D堆叠。 所以3D堆叠还是适合storage、memory、缓存甚至是IO等完全横向扩展且功耗发热不集中的应用场合。 |

|

可以是可以,那你觉得TDP应该几千瓦呢? 另外本来就严重的积热问题你想好怎么解决了吗 |

|

|

虽然 SSD(固态硬盘)可以使用堆叠技术来增加存储容量,但CPU(中央处理器)不能简单地通过堆叠来提高性能。 CPU 是一个高度复杂的芯片,它包含了数十亿个晶体管和其他电路元件,这些元件需要在非常小的尺寸上进行精确的布局和连接。堆叠更多的 CPU 层会增加制造的复杂性和成本,并且可能会导致更高的故障率和热量问题。 此外,CPU 的性能不仅仅取决于芯片的数量,还受到许多其他因素的影响,如时钟频率、核心数量、缓存大小、指令集架构等。通过改进这些方面,可以在不增加芯片数量的情况下提高 CPU 的性能。 因此,虽然堆叠技术在某些情况下可以提高存储容量,但它并不是提高 CPU 性能的有效方法。相反,CPU 制造商通常会采用其他技术来提高性能,例如增加核心数量、提高时钟频率、优化指令集架构等。 |

|

|

除了堆叠技术,还有以下几种方法可以提高 CPU 的性能: 1. 增加核心数量:通过在 CPU 中添加更多的核心,可以同时处理更多的任务,从而提高性能。 2. 提高时钟频率:提高 CPU 的时钟频率可以使其更快地执行指令,从而提高性能。 3. 优化指令集架构:通过改进 CPU 的指令集架构,可以使其更高效地执行指令,从而提高性能。 4. 增加缓存大小:增加 CPU 的缓存大小可以减少访问内存的次数,从而提高性能。 5. 使用更先进的制造工艺:使用更先进的制造工艺可以减小芯片的尺寸,提高集成度,从而提高性能。 6. 采用多核技术:多核技术可以将多个 CPU 核心集成在一个芯片上,从而提高性能。 7. 采用超线程技术:超线程技术可以让一个 CPU 核心同时处理两个线程,从而提高性能。 需要注意的是,这些方法都有其局限性和成本考虑,CPU 制造商需要在性能、功耗、成本等方面进行权衡和优化,以满足不同用户的需求。 |

|

|

|

|

cpu确实能靠增加数量提升性能,这不是废话 苹果的M1 Ultra芯片,就是把两块M1横着排在一起 但是你猜他为什么不叠起来放... |

|

想法很好,问题是散热做不到。 |

|

人均分体水甚至压缩机的时代,到来了。 |

|

查一下CPU的历史很难吗? 以前的CPU就是单核的,为了提升性能搞出来了多核技术。当初AMD和Intel打架的时候,Intel就被吐槽是胶水双核。 |

|

|

| [收藏本文] 【下载本文】 |

| 上一篇文章 下一篇文章 查看所有文章 |

|

|

|

|

娱乐生活:

电影票房

娱乐圈

娱乐

弱智

火研

中华城市

印度

仙家

六爻

佛门

风水

古钱币交流专用

钓鱼

双色球

航空母舰

网球

乒乓球

中国女排

足球

nba

中超

跑步

象棋

体操

戒色

上海男科

80后

足球: 曼城 利物浦队 托特纳姆热刺 皇家马德里 尤文图斯 罗马 拉齐奥 米兰 里昂 巴黎圣日尔曼 曼联 |

| 网站联系: qq:121756557 email:121756557@qq.com 知识库 |