| |

| ֪ʶ�� -> ���� -> оƬΪʲô�������������أ� -> �����Ķ� |

|

|

[����]оƬΪʲô�������������أ� |

| [�ղر���] �����ر��ġ� |

|

��ɶ����������Ҫ�磬���������ʵģ���Ȼ��̾���7����10���ĺ��ѣ�Ϊɶ����оƬ���������أ����������ô��ϸ�ĵ�����������������ô��飬����㡭 |

|

оƬԽ��ʱ�������ʱ�����ṹԽ���ӣ����ֲ���ʱ����ʱ��ƫ�ƵĿ���Խ�ߣ���ż���ҲԽ������������ҲԽ���ӣ��Կ�ʴΪ��������ʮ���磬Խ��edge�ĵط�profileԽ������������Ӵ�wafer�ߴ磬����������Ѿ��Ⱥ��wafer���棬ͬʱ��̨�ߴ������Ҳ������fabռ�����ӣ�����Ӱ��fab����������Ҫ������ԣ��������Ϻ;����϶��в�С�����⣬������ |

|

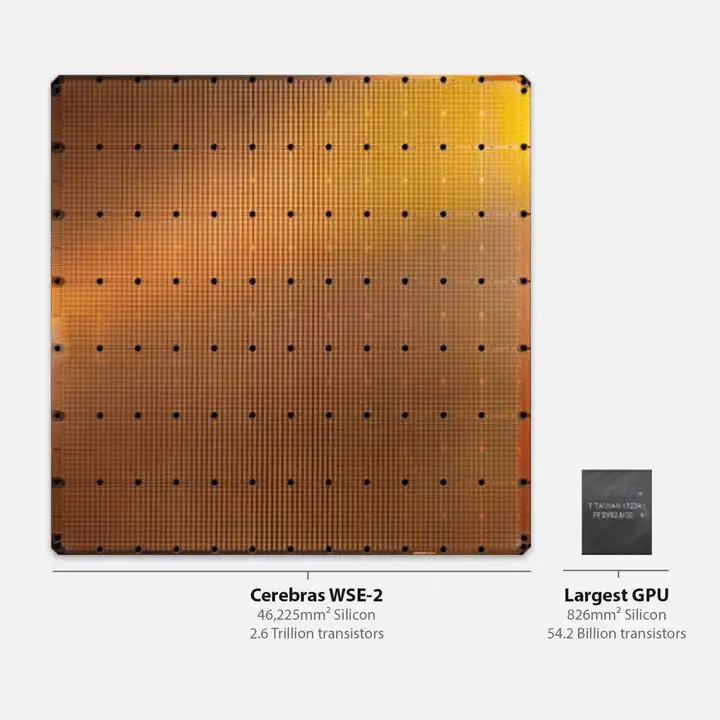

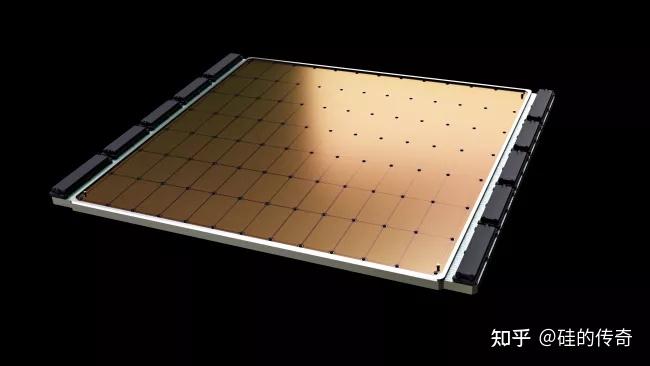

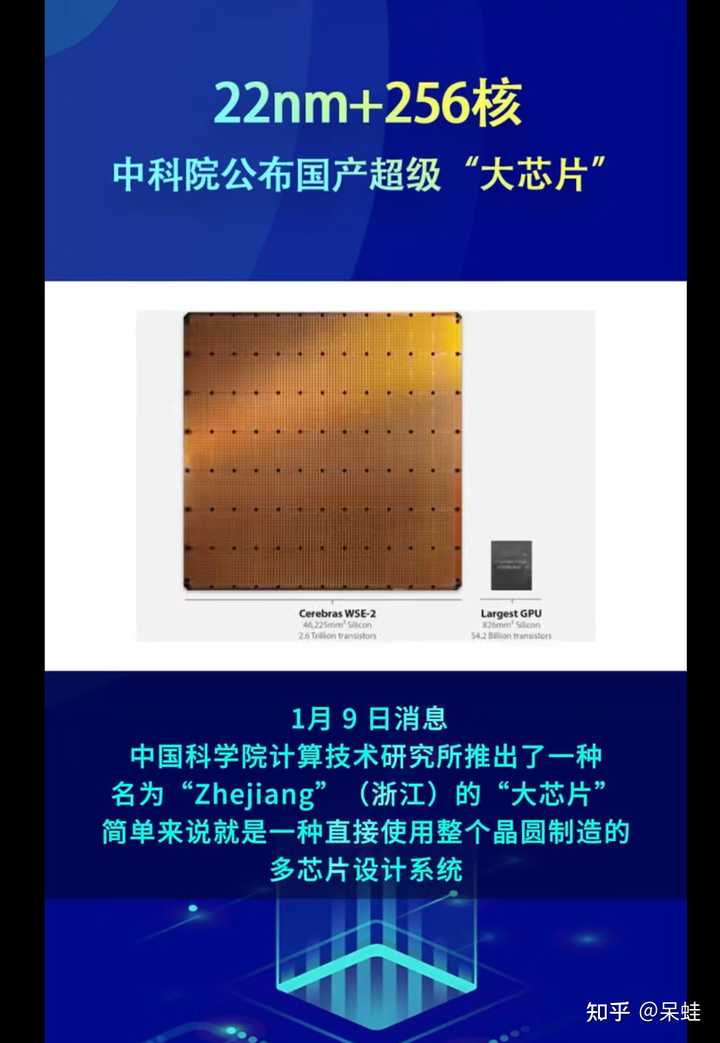

Ŀǰ����оƬ��cerebras��˾��Ƶ�WSE-2оƬ��ר��Ϊͼ��ʶ���AIѵ������ģ��ߴ絽��46225mm2�� ����7nm�Ƴ̹��գ���ֱ����һ���鷽�εľ�Բ��ʴ�ɵġ�һƬ��Բ��ֻ����һ��WSE-2оƬ����С�dz���оƬ�����ٱ������й���15KW��һ��оƬ�ϼ�����2.6���ڸ�7nm����ܣ���װ��850000���ں˺�40GB�ڴ档 |

|

|

WSE-2оƬ����ͨоƬ�Ĵ�С�Ա� ����Ȥ�Ŀ��Ե����ǹ������£�Product - Chip - Cerebras ֻ��˵�������һ������յ���������Ʒ ________ ��һ��оƬ��ʵ��С�Ķ���ͼ |

|

|

|

|

�� |

|

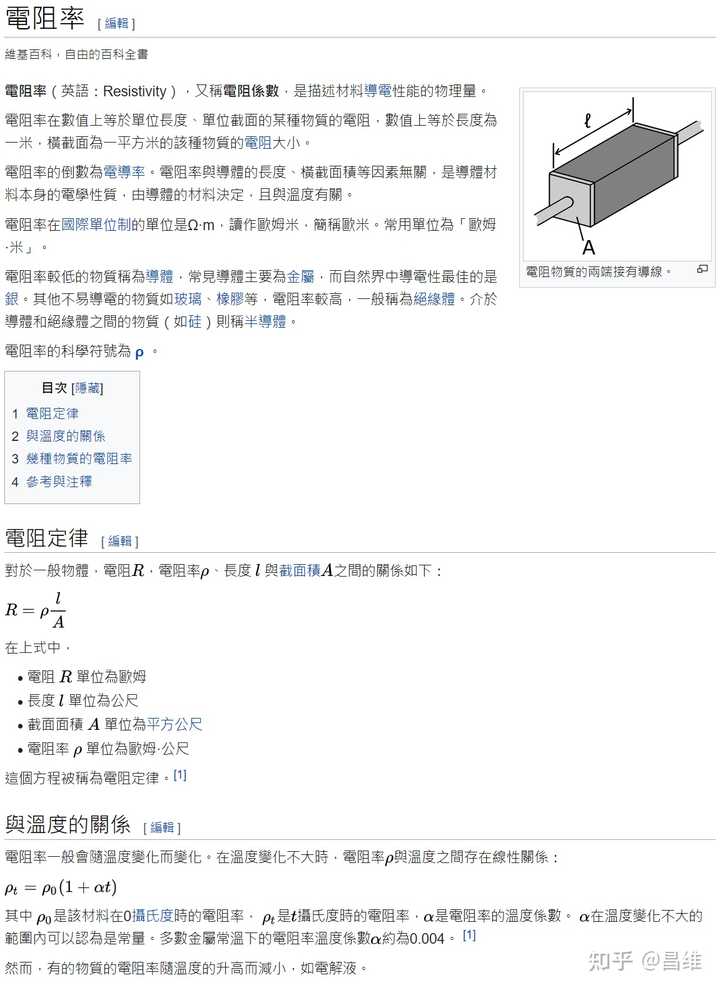

���ǵ��ݼ��㹫ʽ �ӹ�ʽ���Կ������ݵ���ֵ�ܵ����ʣ���糣�������������棬���缫����Ȳ����й� |

|

|

��оƬ������ʱ���������ݵ���ֵ����������RCʱ�䳣��\tao RC��·ʱ�䳣�����ӣ�RC RCʱ�䳣����ᵼ�¾�����ڿ��ٿ���ʱ�����ż���ѹ���ż���ѹָ����TTL����CMOS��ƽ���й涨��0��1����Ӧ�ĵ�ѹֵ�����ٶȱ���������Ӱ��оƬ�������ٶȡ� ���ǵ��趨���Լ��乫ʽ���ӹ�ʽ���Կ���������ܵ������ʣ�������¶ȵ�Ӱ�� |

|

|

��оƬ������ʱ�����ŵ�Ԫ֮��IJ��ߵ������������оƬ���������ӣ������ݵ�����¶ȱ仯�����������¶ȱ��ʱ�����ֻ��һ�����ӣ����¶���ѭ���� ����������оƬ�����С���Խ��ͷ��ȣ��������ܣ������ΪʲôоƬҪ���ϳ���С�����Ŀ�귢չ��ԭ�� |

|

Զ��ʱ���Ķ������ź��ٶ���10��/�룬���Զ���������1�ס����纣Ы�ӡ������Ϊ��ͷβ�ź�ͬ���� ���������������������һ��֬����㣬���˼������������й����������ź��ٶȴ�100��/�뼶�����Զ�����Դﵽ��ʮ�״�С�� cpu����Ƶ�ʾ����������������� |

|

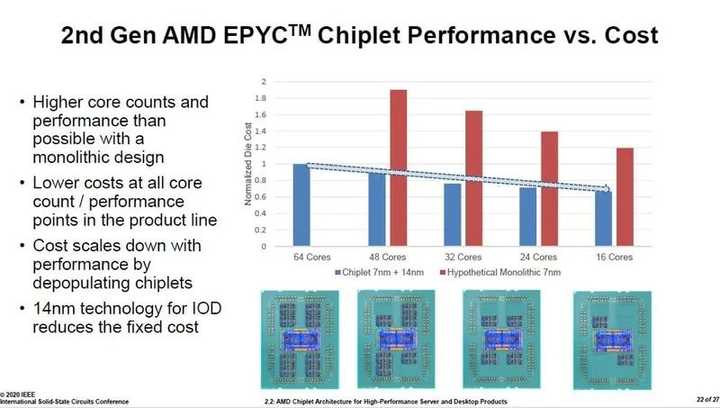

�а����㿴amd���ķ�����cpu������������һ�����˰�����ô���Ե������ӳ�ȥ���ˡ�����֮ǰintelҲ��������ĵ�cpu, ��ʵ�ǿ��Եģ���������������ĺͲ��϶��˷����أ������˼���ôǮ��? |

|

���õĶ������Ǿ���������Ŀ�꣺���ܺͳɱ��������������������Dz����ġ� �����ϣ����ڴ��ģ���ɵ�·��������MOS����Ϊ�����ģ�MOS������м����ĵ��ݣ���MOS����ܹ�����ʱ����Щ�������ݻᱻ��ŵ磬ѧ��������·֪ʶ���˻�֪�������ݵij�ŵ�����Ҫʱ��ģ���MOS����������ʱ�������ݻ��������ŵ��ʱ��Ҳ��䳤�����ԣ������Լ�˼��ɵ�·�Ĺ���Ƶ�ʣ�Ҳ����������Ե�ʱ��cpu��Ƶ�ʣ���Ҷ�ϣ����Ƶ�ʸߵģ���Ϊ�ٶȿ졣����ײ�MOS������ŵ��ʱ���������ô���ݵij�ŵ�ϲ��ϸ�Ƶ��ת������·���ܾͻ������⡣ �ٴӳɱ������������ɵ�·���������У����յ�defect����particle��Ӱ�죬�������ʽ��͡�Ҳ������Щ�������䵽��оƬ���ͻ��Ϊ����Ʒ����оƬ������ʱ�����оƬ��Ϊ����Ʒ�ĸ��ʾߣ���Ϊ���������Ļ���ߡ�����оƬ��������ʾͻ��ͣ����Գɱ��������� ���ϡ� |

|

|

Frank 103 ����ѯ 5.0 4196 ����ͬ ȥ��ѯ |

|

�����ڵĸ�ƵоƬ��˵�������Ѿ��е����� �����˹��ܵĸ��� |

|

���ֻ�ǡ�оƬΪʲô�����������һ�㡱������⣬��ô�����ҿ����DZȽ�ֱ�ӵģ� �������շ���Ȼ����幤���йأ����������ǰ�wafer���շѵġ�������֮��ͬ��������оƬ������ԽС����ôÿƬ��Բ����������оƬ������Խ�࣬��Ʒ�ľ�����Խ�ã��ɱ�Խ�ͣ��� ����ʵҲ��Ϊʲôƻ������������M1 Max��M1 Ultra��ʱ���Ҹп���ԭ��ƻ���ܹ�����ݳ�ʹ���Ƚ��Ƴ̵ľ�Բ�������������ܰ�������оƬ����ͬ��������ն˲�Ʒ�ϲ�������ȥ���������һ�㲻��IC�������ѷɫ�� ��������������������������Ƚ��Ƴ̱������ӣ��ܲ����ó����Ƴ��������оƬ����һ����������⡰����ô����𰸾������ܵ�it depends�� ����Ҫ˵���ǣ����˼·������ȫ�����С��������ѵ��������ر����ֻ������Ƚ��Ƴ���ͻ���ͽ�������ƻ�����µ�A17оƬ�Ѿ�����ȷ��������̨�����3nm�Ƴ̣���ʵ��������Ȼ�д����뵼��оƬʹ�õ���28nm��45nm�������ߵij����Ƴ̡� �����Ƚ��Ƴ̴����ļ������ƣ�����оƬƵ�ʸ��ߡ����ĸ��ͣ��ڳ����Ƴ��ﲢ��һ������ȫ��������ټ��ϳ����Ƴ�����оƬ�������������Ը���ۺ�������Ʒ������ƾͷdz������ˡ� ����Ǵ����г������ij����������ֻ������Ե�����Ʒ���Գɱ�Ҫ��ܸߡ�ͬʱ��Ʒ�����϶Թ��ģ��������ǹ��յ�����888������8����Ԫ����������ֻ��������ԣ�Ҳ�кܸ�Ҫ�����˼·���в�̫ͨ�� ��������dz�������ս��Ŀ�ģ�������ֹ��ڲ�ҵ������������ҵ�����ù���������������Ӧ�ó����������ܡ����ĵ�Ҫ��û����ô�ߣ���ô���������ȷ�ǿ��Գ�Ϊһ�����ѡ��ġ� ����������ش�����221 ��ͬ �� 32 ���ۻش� ʵ���ϣ����������������Ŵ��������ȷ�кܶ�ɹ������ù���������Ը��ߵij����Ƴ̲�Ʒ�������ŷ�����ܸ��ŵIJ�Ʒ������ս�Կ����£��ɱ��������ϵIJ����û����ô��Ҫ�ˡ� |

|

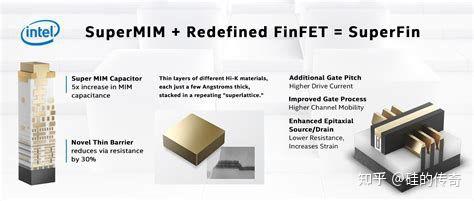

�����ϵ� ��֪��оƬ�������Ƿ��Σ���Բʹ�õ�һЩ�ؼ�����ע����������Բ�� �ã�оƬԽС��������Խ�� ��֪���������覴ó����ھ�Բ�ϣ��������оƬ�������覴ã�оƬ����������Ϊ���� �ã�оƬԽС��覴�Ӱ�췶ΧԽС ��������˼Ϊ��������ʣ�����ռ�г�����ʹ��о����������FPGA�п����죬�ڵ��Ƴ̹�Ƭ��Ϊ�װ����� ���ֳ�����оƬΪ��������ʣ��и��ӵ�������ƣ��˷�оƬ����� Intel��AMD��NVIDIA��оƬ���Ǹ���ʵ����������еȼ����֣�AMDʹ��о���������͵�die��С��������ʣ���ʹ�ö�die��װ���� �����ԽС�����ܼ�������ԽС��Խ�����ϸ�Ƶ�����ο�������Ҫ������Խ�٣� Ϊ��˳������Ƴ̣��Ⱥ�����finfet��superfin���գ��Ѿ���������˻�����ʱ��ס���Ƴ̽��� |

|

|

ĿǰоƬ����������40%ȫ����Դ���Ƴ���������С�ľ���ܣ���ϸ�����߿������Ƶ�ʽ��ͷ��ȣ������յĽṹʱ��Ҳ���Ա�֤ �����14nm+++������ˣ��ø����ϵ�˭��? 14nmͬ��·ͬ�����¶Ⱥ�7nm��༫����28������ ��Ʒ��棺 ��֪������������Ҫʱ�䣬һ����ѹ�ź���Ҫ�Թ������ߵ�Ŀ��� ���Բ�����·��Ҫ��Ƶȳ����ṹ��·��Ҫʱ�����֣���ͬ����ʱ�ӵ��ӳ� ����е�ż������⣬ɢ�ȼ��������⣬�������ߴ������ӳ����⣬�߹��ʶԹ����ɢ��ϵͳ�Ŀ��飬�豸������Ӱ�죬�����Ѷȣ��ź������ԡ��� ���Ƴ̴����ľ���ܼ�ľ���䳤�����оƬ������Ϊ�ɹ۵��ӳ����⣬�������ݣ�������л���������ϵͳ�����ٶȣ�����ʱ�ӻ��ֵ�������������С���ṹ����ɢ������ģ���ű������� ����28nm���������µ�����ܼ۸�û�м�����̽��ֻ���Դ��ģ���÷�̯�������ã�����оƬһ��ʹ��28nm������ɿ� ���⣬���ϵ�wse2ʹ����7nm���գ�������2.6���ڸ�����ܣ�23kw���� |

|

|

���ϵ�wse2 |

|

|

�ȵ��¯��������ɢ�ȷ������г���ʽҺ�䣬�÷���Һ�ͻ��������ȣ��DZ���Һ��ѹ�������� |

|

����˴�Լ20����ش𣬲��Ͽɾ�������𰸡� �����ߵ���������ǰ�������ģ�����Ȼxxxx��Ϊɶ��xxxx��������������Ҫ�Ӽ�����һ�ԵĽǶ����ش�����⣺ ���ǿ϶��ģ�����оƬ����һ�㡣PPA����û���⡣ʵ��ͬ�ȹ��ܣ����IJ�����������Ҳ�����ӻ�����������������߲��������������һ���ڹ��̼���������Ը����ף�˵���������Դ�������ĺô��� ���ң���ʵ�������кܶ���Ҫ�����оƬ�������ij�����оƬ������ԽСԽ�á� ���ڳ�����ܵ���оƬԽ��ԽС�������Ͻ��ؽ�����ijһ�������оƬԽ��ԽС�ĸ���ԭ����Ӧ�����������Ǿ��������ġ� �ܶණ����������̫��оƬ������������γߴ�ܿ���Ҳ���ű����������ϵ�������Ʒ��һ������ԭ����Ҫ��Ӧ�������������ߴ��Լ����Ƶķ����ԡ����磬�ֻ��ijߴ�͵÷��������ã�оƬСһЩ���á��ȵȣ�����Ӧ�ó������������ӡ� ������������������Ҳ�����Լ������ӡ����磬��ҵ�ڵ���֪������ЩоƬ��0.25um��������ȫû�����⣬�������ڲ�ҵ��ģЧӦ��ֻ�ܸ����������ղ���ʵ�ֳɱ�Ч�����������ͱ������110nm����55nm�Ĺ��������ˡ���ǰ�ƽ�������ʵ�����˺ܶ����Ĺ������������ĽǶ���ȫû�б�Ҫ��С�� ��۵ĽǶ��������ﵽ��ǰ������������ˮƽ�����ṹ����ȫ���Բ��ù蹤�հ뵼����һ��·������������̹�����ȫ�ء����ǣ���Ȼ���ȷ�����PN�ᣬ�Ѿ�������һ��·�������ͷ�Dz����ܵġ�����ԭ���Ǿ���ԭ����˵�����������֯�ṹ��ԭ�� �Һã���̹����Ѿ��쵽ͷ�ˡ�δ��3-5�� 2nm�ض�������Ȼ�����ǻ���һ���µ�·����Ҳ����˵��оƬ������Խ��ԽС�ˡ�Ϊʲô����оƬ����һ���أ������ع������ߵ����⡣ ǧ������Ϊ��״��������Ȼ�ģ��Ӷ���ɱ���½����ߵĴ����ԡ�����²�ֹһ������ |

|

�ţ�ԭ���кܶ࣬����������Ʒ��������Ÿ���������������˵������˼�ĵ�ɣ��������ޣ����µ�ʱ��ƫ�ơ� ����Ϊ3x10^8��/�롣 �ִ�CPU����ƵΪ5GHz��Ҳ����˵����ʱ�����ڳ���Ϊ1�£�5x10^9��=2��10^��-10���롣 ���ʱ���ڣ����źţ����٣��߹���·��Ϊ2��3��10^��-2���ף�Ҳ����6���ס� ������һ����ƵΪ5GHz��оƬ�ϣ����Ϊ6cm���������֣���ͬһʱ�̣�����������ͬ�������ڡ� ���е�������ʱ�����9��11��ʱ���й�������9��12�ţ� ��ˣ��������Խ���оƬ��ʱ���ٶȾͲ��ܵ���̫�ߣ���������˵�ġ�ʱ����ø����ԣ���ʱ���ٶȵ��ˣ�оƬ�ļ�������Ҳ�͵��ˡ� ������С��оƬ��������������ЧӦ������ľ�������������ޣ�����������Ҳ�������ˡ� ��Σ��Ƿ����ֱ���ά�����á����١������˿Ƽ��Ŀ־�У� ��Ȼ��ʵ��Ӧ���й���ʦ�ǿ���ͨ��ȫ��ʱ���������Ϊ�����ӳ٣���������������֡�ʱ���Ӱ�졣�����Խ�����֡�ʱ���Խ���ԣ����ԣ�����оƬ��С ������ʱ���Ӱ�죬�������������� |

|

��֪��Բ��Բ�� оƬ�������Ƿ��� ������Խ���˷�Խ������ɵļ۸�Խ�ߣ��ټ���һ�������̶��ijɹ��ʣ�����ȥ��⣬һ�廵һ��������ͷ�� ��˾������ô���ģ���Ʒ������ôȥ��Ƶ� ������ʲô������������оƬ����������۸� |

|

�뵼�峧��Cerabras Systems��չʾ��һ������������оƬ����WSE��Wafer Scale Engine������оƬ��Cerabras������������Դ������������CS-1��AI������ϵͳ�������ۼ���200�����ҡ� |

|

|

|

|

|

оƬ����Ĵ�С�ǿ�������ģ����ǻ��кܶ�����⡣оƬ����Ĵ�С�����ʱ��Ҫ�����������أ����ܽ�оƬ���������ܻ����һ�������ƣ����Ⲣ����һ���Ľ��������������һЩӰ��оƬ���ѡ��Ĺؼ����أ� 1. ���ܣ����ž���ܳߴ����С�����ɵ�·�����ܵõ���������������С�ľ���ܿ����ڸ��͵ĵ�ѹ�¹������Ӷ������ġ����⣬��С�ľ������ζ���źŴ���������̣���˴����ӳ�Ҳ���С���Ӷ����оƬ�������ٶȡ���оƬ���������ܻᵼ���źŴ����ӳ����ӣ��Ӷ��������ܡ� 2. ���ģ������оƬ��������ܻ����ӹ��ġ�����ܵijߴ�ԽС��©������ԽС������ҲԽ�͡��෴�������оƬ������ʵ��ͬ���Ĺ������ơ� 3. ɢ�ȣ�����оƬ���������ɢ��������ܻ��ø����ء���Ϊ��������оƬ���ܻ�����������������ɢ��ϵͳ����ƽ���ø��Ӹ��ӺͰ��� 4. �ɱ�����Բ�������ɱ������ž�Ƭ��������Ӷ����ӣ�ͬʱ������оƬ��ȱ����Ҳ���ܻ���ߣ�������Ʒ���½��� 5. �������ƣ�����Ŀǰ�İ뵼�幤�����Ƴ̳ߴ����Ѿ�ȡ���˷dz����ͻ�ƣ������������ߴ�оƬ�Ĺ�������Ȼ�������༼����ս�����磬��Ƭ�Ļ������Ӷȿ��ܻ����ųߴ�����Ӷ����ӣ���ᵼ����ƺ���֤���̱�ø������ѡ� Ŀǰ�������ִ����Ӳ�Ʒ��оƬ��Ҫ������϶���ԽС�Ŀռ�ʵ�ָ���Ĺ��ܡ����ض�Ӧ����һ�㲻��������ô���� |

|

������岻����Ϊ���ǵ�ɢ�ȣ��������⣬��оƬ�ĵ�·�Ǻܱ���Ƭ״���Ȼ���ڹ��ıȽϵ͵�����оƬ����ʹ�ö�㣬��ʵ����Ҳ�DZ�Ƭ�� ����������岻���������������� |

|

|

|

|

|

��֮ǰҲ˼�����������⣬�����þ�Բ���ĸ�����λ��������оƬ����Χ����С�ģ����������ʿ��������� һ�龧Բ�Ͽ���������ͬоƬ��?www.zhihu.com/question/568018481/answer/2768741902?utm_campaign=&utm_medium=social&utm_oi=683206044646379520&utm_psn=1691125601652592640&utm_source=zhihu |

|

|

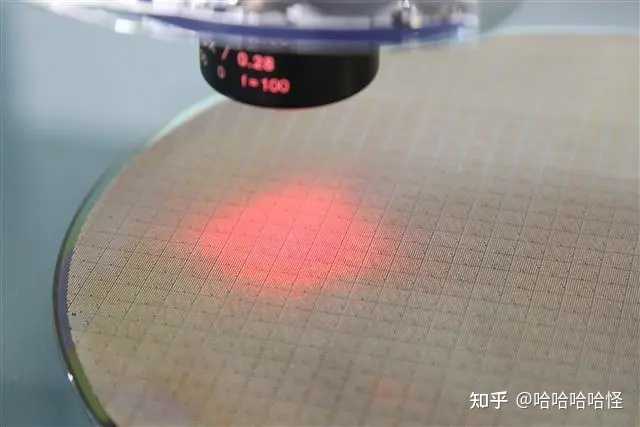

ͨ������ѧ��һ��С֪ʶ�����ǹ�̻�������ع����� �Ƚ�����-ɨ��ʽ��̻�����֧�ֵ�����ع�����(exposure field)�����26mm��33mm�� ����ʽ��̻�(stepper)���ع�����ֻ��22mm��22mm�� ��������������26*33=858��һ��ֻ��Ӣΰ�����߶�GPU��Ӣ�ض���IBM�ķ�����оƬ�Ż�ӽ�����ߴ磬�����оƬ�øĹ�̻��� оƬ�ɱ�������O������ζ���������������оƬ�ɱ��Ǽ��������ġ� �����Ҳ��˼��һЩ����оƬ�����⣬������оƬ�ĵ�һ���۱��� ���˾��ò��ǣ���Ч�����Ч�ʸ��ؼ��� ��Ч���������ܹ��������ϣ�������ǹ�����ɢ�ȣ���ʵ��ʹ���еijɱ��� ֻ�����ܣ���ǿ����Ȼ��Ӣ�ض��Ŀ������zen2��ʼ��AMD���ڲ��ϲ�ʳӢ�ض����г��ˡ� |

|

|

|

|

��Ҫ��ʲô�ط��ģ�̨ʽ���Ͳ������ֻ����ּ�NM��оƬ������оƬ�����ϱ��֣��ȶ����ǵ�һҪ�� |

|

���������лش𣬶�û�лش��ϡ���Ϊreticle size limit�����ǹ�̻����ֵļ��ޡ� |

|

|

|

|

оƬ����������������оƬ�ڲ������ļ��ɵ�·�йأ�Խ�Ǹ��ӵ�оƬ�����ļ��ɵ�·��Խ�ࡣ ������ڹ�������������ôоƬ�����������ͻ�����Ħ������һ����ÿ��18��������һ���� �ڵ�λ�ܺIJ��������£����Խ���оƬ�Ĺ���Ҳ���ƺ���Ϊͬ������һ��������Ҫ���ǣ�����оƬ�Ĺ�Ƭ��Ƭ����һ���ģ�һ���Ƭ�����и����оƬ����оƬ������Ƿ��ȡ�����оƬ���Խ������оƬ�ijɱ���Խ�ߣ�ͬʱоƬ���ܺ�Ҳ��Խ�� �����ܺ��������ͨ�����Ͻ����Ĺ������������ɱ��������������·���ˣ�Ҳ�����ֲƴ����ֵ���ҵ������Ȳ��ۣ�������Ǯ������ƻ����˾����������Mϵ�е�оƬ�����ж�оƬ���ϵ�pro�汾��Ultra�汾��MоƬ�� |

|

�Ѿ����������·�������� ����3d�ѵ��Ѿ���memory�Ϲ㷺Ӧ�ã�socҲ��ʼ����2.5D��װ���ա� |

|

ר��оƬ������Ҫ���ܶ��ͷ�����ͺܴ� �����ֻ�����ͨ�ʼDZ���������ô���ǵģ���ΪӰ���û�����������ǵ��˼������ܣ������Ƕ���ܷ����ܡ�������ߵ������ܣ�Ŀǰ����Ч�ķ��������������Ƚ����Ƴ̡� ����ʹ�����µ��Ƴ̣���Ȼ�й��ʵ�һϵ�еĿ��ǣ�����һ���ȵĻ��ǵ������ܣ��������ܻ����ܾ����û��ڴֳ����µ�ʹ�����顣 |

|

����оƬ��˵�������������һ���Ǹ��õ�ѡ����ΪоƬ���������Ҳ�����һϵ�����⡣ ���ȣ��������������оƬ�������Ѷ�Ҳ�����ӣ���Ҫ���ߵ�����ɱ����ߵļ���ˮƽ������ܻᵼ��оƬ�۸���������������ڵ��ӳ��� ��Σ�����������ᵼ��ɢ�����⣬��Ϊ�����оƬ��Ҫ�����ɢ���������ܱ����ȶ����С��������Ҫ�����ɢ����������ķ��Ȼ�����ɢ�ȼ�������Щ�������ӳɱ�������� ���⣬����оƬ������������ǵ��ܺ�Ҳ�����ӡ�����ζ����Ҫ����ĵ�Դ���õĵ�Դ����������оƬ���ܻ���Ȼ���������ʱ�����ȶ������⡣ ������ƶ��豸�������ռ����ij��ϣ�����оƬ������ܻ����Ʋ�Ʒ����ƿռ䣬���������豸������������� ��ˣ�оƬ������ͨ����Ŭ���ڱ��ֽ�С�ߴ��ǰ���£����оƬ���ܺ���Ч�ʣ������ǽ���ͨ�����������������ܡ���Ȼ������ijЩӦ�ó�����˵���������оƬ���ܻ�������ƣ�������Ҫ���ߵļ������ܡ�����Ĵ洢����������ӵĵ�·��ơ����ǣ����ձ������£�С�����оƬ���������г����������ɱ���Ҫ�� |

|

�ɱ�̫�� |

|

�Ѿ������ˣ���ǰCPU�������εģ��������泤������һ�ؾ��������˵ġ� |

|

|

2024�긽�� ��������ˣ�������Բ��оƬ�� |

|

|

|

|

��������ĵ�cpu�����dzɱ��ϲ����㡣��Ҫ������Ҳ������ϵͳ���Ÿ����оƬ��ʵ�ְ�����������ʵ������Ҫ�ɿ��ͳɱ��Ķࡣ |

|

�������������ָ�� GTX4090��5nm��450W�������28nm������һ�£�оƬ�������31����������ô�������оƬ���ǿ�������������Ҫ����14kW��˭�ҵ���ܴ���������һ��������Ϸ��ʱ���Ա߰���10̨��ů�����û��˵CPU�Լ������Դ��ɢ�ȡ� |

|

����˵���Dz��ǣ�����оƬ ���������100+���ģ����ϴ�һ����Ƥʵ��һ���������Ҳ�dz��� �����ϸ���˵�������оƬӦ����һ�ѵ��ӹܣ���������Ӵ�û�Ǵ��Ļ�����ĵ���Ҫռ���������䣬�����ٶȻ��������ڴ����10��Ǯһ���ļ���� |

|

һ��300mmֱ���ľ�Բ��16nm���տ�������100��оƬ��10nm���տ�������210��оƬ�����Ǽ۸�ͱ�����һ�룬���г��Ͼ���������ס�������֣���Ǯ�ֿ����������з���������ô�����ˡ� ������а�оƬ���ø�С�ļ����������Ͻ���Ǯ�� ˵�����⻰���й�����оƬ����ʵ�����Ը����㣬�������ܸܸܵģ���Ϊ���ò��ƽ�Ǯ�����оƬ���Ĵ��ģ���Ϊ��IJ����ð��������⣬Խ��Ĺ�Ƭ�������ʵĸ���Խ������оƬԽ����Ʒ��Խ�͡��ܵ���˵����оƬ�ijɱ�ԶԶ����СоƬ�������Ծ�����˵���ⶼ�����¶��� ���˳ɱ�֮�⣬��оƬ�IJ��߱�СоƬ������������ʱҲ�����ԣ���������Ҳ��ܶ࣬�ɴ˵���������Ƹ�ӷ�ף������ϻ��ǻ�Կ���������СоƬ���DZȴ�оƬ���á� |

|

|

����ôһ�죬������18000ֻ���ӹܣ�6000�����أ�7000ֻ���裬10000ֻ���ݣ�50�����������һ���������ӵĵ�·�������������һ̨��������ش�30�֣���������5000��/�룬�����������ֳּ�������ʮ��֮һ����֪����ʱ�Ĺ���ʦΪ�˰�װ��ѵ�·�����ӳ���˶��ٻء� |

|

|

��������˼·�ͼ��ˣ���ΰ���30�ֶ��������ɵ�ָ����ô��ĵط����أ������оƬ�� оƬ�ӹ������Ѿ�����7nm����Ȼ���Ǵ�ţ˵Ҫ�յ�3nm����������Σ��㻹�ܼ�������1nm�����Ǽ���ԭ�Ӷ��ѣ�����ЧӦ�dz���������Ϊ��ʯ���ܴ����۾Ͳ���ʹ�ˣ��뵼����ҵ�͵������Ъ�ˡ� |

|

|

��ǮҲ�ã���ʱ��Ҳ�գ��յ���ͷ��������������������ѧ������Ǯ��ʱ�䣬�������ˣ��յ��쳣���ң�100�������̣�99�����ǵ��ʯ������ʦ��������ң�������ѧ�ұ���ư������ ���ܹ����ڵ����ˣ�Ϊ�˰�����Ҳ���������۸Ͻ����ƣ��������ԣ��Ǻ������ຢ��ѧ������ѧ�ɣ� |

|

����������ζ�Ÿ���Ĺ��ġ� ����Ĺ�����ζ�ŷ�������Ⱥ����ĵ�Ƥ�Ѻ͵��֧�����ֻ�����ĵ�ظ��̵�������̨ʽ�������ɢ�Ⱥ������� ��оƬ�Ĺ˿Ͳ�ϲ����������Щ���������ࡣ |

|

�Ѿ�Բ����һ��A4ֽ�� ��С�ǹ̶��ġ� ��д��Խ���ֵԽ�ߣ� �ǵ�Ȼ����д��ԽСԽ�ã� һ��ֻֽдһ���ֲ��Dz����ԣ� ���Ǿ�����û�о����� |

|

����һ�龧Բ���Ϊ100����λ���ɱ�Ϊ100Ԫ����ô��һ�������λ80%���ʵ�����£�һ�����Ϊһ����λ��оƬ�ɱ�Ϊ100/(100*80%)=1.25Ԫ һ�����Ϊ������λ��оƬ�ɱ�Ϊ 100 / (80% * 80% * 50)= 3.125Ԫ ���ŵ���оƬ�������оƬ��ʵ�ʳɱ���ָ������������ |

|

|

| [�ղر���] �����ر��ġ� |

| ���� �������� |

| ��Ϊ�Լ��з���оƬΪʲôȴԽ��Խ���ˣ� |

| Beats �ڱ�ƻ���չ����䡸���ơ������Ƿ� |

| С��˿Ϊʲô���������ˣ��������֮�� |

| �� 3 �¹����г��ֻ������� 2115 ��ͬ�� |

| Ϊʲô��ѩҪ���ҴҰ��Լ����Լ��Ļ���Ʒ�� |

| �������MacBook Neo�� |

| Ϊʲô�ֻ���BL����������û���أ� |

| С��14Ultra�����ٶȱȻ�ΪMate60pro���죬 |

| ��ο��� 3999 Ԫ���۵� OPPO Find X7 ϵ�� |

| ��Ϊ�ֻ����������һ�������Dz����Բ���� |

| ��һƪ���� ��һƪ���� �鿴�������� |

|

|

|

|

��������:

��ӰƱ��

����Ȧ

����

����

����

�����

ӡ��

�ɼ�

��س

����

��ˮ

��Ǯ�ҽ���ר��

����

˫ɫ��

����ĸ��

����

ƹ����

�й�Ů��

����

nba

�г�

�ܲ�

����

���

��ɫ

�Ϻ��п�

80��

����: ���� �����ֶ� ������ķ�ȴ� �ʼ������� ����ͼ˹ ���� ����� ���� �ﰺ ����ʥ�ն��� ���� |

| ��վ��ϵ: qq:121756557 email:121756557@qq.com ֪ʶ�� |